#### METROLOGY AND MEASUREMENT SYSTEMS

Index 330930, ISSN 0860-8229 www.metrology.pg.gda.pl

# COMPARISON OF INTERPOLATORS USED FOR TIME-INTERVAL MEASUREMENT SYSTEMS BASED ON MULTIPLE-TAPPED DELAY LINE

## Dariusz Chaberski, Robert Frankowski, Maciej Gurski, Marek Zieliński

Nicolaus Copernicus University, Faculty of Physics, Astronomy and Informatics, Grudziądzka 5, 87-100 Toruń, Poland (

daras@fizyka.umk.pl, +48 56 611 2417, robef@fizyka.umk.pl, gural@fizyka.umk.pl, marziel@fizyka.umk.pl)

#### Abstract

The paper describes the construction, operation and test results of three most popular interpolators from a viewpoint of *time-interval* (TI) measurement systems consisting of many *tapped-delay lines* (TDLs) and registering pulses of a wide-range changeable intensity. The comparison criteria include the maximum intensity of registered *time stamps* (TSs), the dependency of interpolator characteristic on the registered TSs' intensity, the need of using either two counters or a mutually-complementing pair counter-register for extending a measurement range, the need of calculating offsets between TDL inputs and the dependency of a resolution increase on the number of used TDL segments. This work also contains conclusions about a range of applications, usefulness and methods of employing each described TI interpolator. The presented experimental results bring new facts that can be used by the designers who implement precise time delays in the *field-programmable gate arrays* (FPGA).

Keywords: time interval, multiple-tapped delay line, quantization-and-nonlinearity minimization, FPGA, time-to-digital converter.

© 2017 Polish Academy of Sciences. All rights reserved

#### 1. Introduction

The task of a TI interpolator is to increase resolution of TI measurements. It simply reduces to the measurement of a distance between one chosen type of edge (usually the rising edge) of a signal and the beginning of the standard-clock period that directly precedes this edge. A typical TI interpolator consists of one or two TDLs and a register [1–4]. The way the register and TDL(s) are connected determines the way of TI interpolator operation and its use in the system.

Time-to-digital converters (TDCs) can have many applications and can be constructed in many ways [1, 5–16]. TDCs can be used directly or indirectly to measure other quantities by converting them temporarily to TIs. Depending on a use domain and implementation technology TDCs can vary in properties and can differ in cost. The most important parameters of TDCs are: a resolution of TI measurement, a measurement range and a maximum intensity of registered TSs [1, 4].

A measurement resolution of TDC can be improved by applying the Vernier method, interpolation and multiple-stage interpolation, time stretching or multiple measurement [1, 4]. The first three mentioned methods use TDLs and the TDC resolution is determined by the TDL segment delay value. The TDL segment delay value can be decreased by changing the implementation technology to a finer one. The time stretching strongly decreases the maximum intensity of registered TSs but can be applied in conjunction with any other method. The multiple measurement can also be used jointly with any other method and can be performed either in parallel or sequentially [17, 18]. When the multiple measurement is carried out in parallel there is no need to duplicate the whole meter. For TDL-based TDC only TDLs, codeconverters and memory blocks have to be duplicated. In that case it can also be called

as multiple-TDL (MTDL)-based one. When the multiple measurement of TI is performed sequentially, only a TI repetition block must be added to the measurement module.

A measurement-range can be extended by implementation of a standard-clock period counter, but it is limited by the long-term standard-clock stability. The maximum intensity of registered TSs usually can be increased either by parallelization of critical TDC blocks or by changing the implementation technology to a faster one [19].

Currently the FPGA and *Application Specific Integrated Circuit* (ASIC) are two technologies that play an important role in implementation of TDC. Both these technologies enable to implement regularly placed elements of equal delay that are necessary to construct TDLs [6, 7, 9–12, 19, 20].

When the multiple measurement is used, the correlation of measurement results plays an important role. If the measurement results are not correlated, the average value of standard deviation of n measurements is decreased  $\sqrt{n}$  times. If they are correlated, the correlation degree and its nature should be considered. Highly correlated measurement results enable to obtain more precise information about the real value – in comparison with those totally uncorrelated measurements – when each measurement complements any other one [17, 18]. The way of using TDLs in this paper takes just advantage of this.

The results and conclusions contained in this paper can be useful for the designers who implement and use time delays in FGPA structures. It mainly concerns TI generation systems as well as TI measurement ones. In the literature one can find information about the influence of FPGA structure temperature deviations on the time delay of some FPGA primitives, such as *look-up-tables* (LUT). However, the influence of a clock frequency on the FPGA element delay value has not yet been published. We have noticed this effect during activation of a high-resolution TI generator (an incremental resolution of 1 *ps*) based on TDLs constructed of LUTs, so we have decided to check whether a similar effect would appear in the case of TI measurement systems. We suspect that this effect would play an important role in ring oscillators equipped with the enable input. When a ring oscillator has been enabled (started), the structure it has been implemented in is warming up, so a frequency of the generated clock decreases till the temperature is stabilized.

#### 2. Characterization of tested interpolators

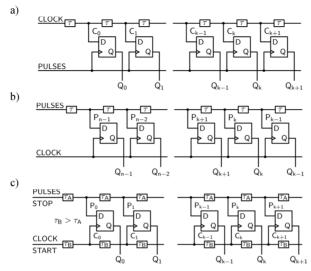

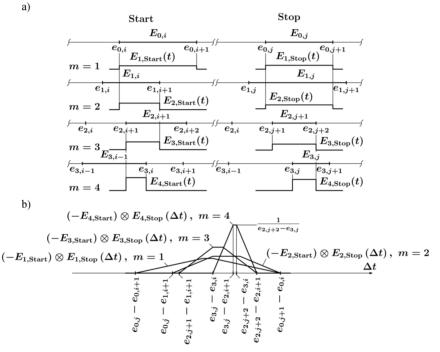

There are many different ways of connecting TDL(s) and a register in order to obtain the possibility of TI interpolating. Fig. 1 shows the three ones tested by the authors. The first TI interpolator (Fig. 1a) registers the state of TDL every rising edge of PULSES signal. The resolution of this interpolator depends on the TDL segment delay values [1, 19, 21]. It is very convenient for this type of interpolator that the delay values of n-1 TDL segments  $(\tau_i, i \in [0, n-2])$  directly create n-1 interpolator characteristic bins (quantization steps,  $q_i, i \in [0, n-2]$ ), but the n-1-th TI interpolator quantization step is equal to the difference between the standard-clock period T and the sum of just mentioned n-1 bin values, so:

$$q_{n-1} = T - \sum_{i=0}^{n-2} \tau_i \ . \tag{1}$$

In this case, when the TI characteristic changes, the number of quantization steps is constant. This fact simplifies the construction of further data processing blocks.

Fig. 1. Three types of tested TI interpolators. PULSES signal registers the TDL state that represents the phase of CLOCK (a); the TDL state that stores the history of PULSES signal is registered periodically (every CLOCK cycle) (b); STOP signal *chases* START signal (c).

The second tested TI interpolator (Fig. 1b) stores the history of PULSES signal in the TDL. This history is periodically (every rising edge of CLOCK signal) written to the register and then – if necessary (the chosen edge of PULSES signal appeared) – further written to memory. Please notice that in this case the register and memory write-ins are synchronized with the CLOCK signal rising edge. In the first type of tested TI interpolator the register and memory write-ins are non-synchronous with CLOCK signal and synchronous with PULSES signal. This implicates that extension of a measuring range of this type of interpolator demands either a Grey code counter (in this case the error is equal maximally to 1 and can be corrected later), two natural-binary counters or a mutually-complementing pair counter-register (in these both cases either the first or the second counter or either the counter or the register contains a proper state) [22]. To extend a measuring range of the second type of TI interpolator (Fig. 1b) only one binary counter is sufficient. The third type of TI interpolator register and memory write-ins are also (as it was in the case of the second type of tested interpolator) synchronized with CLOCK signal, so here also one binary counter suffices to extend the range of measurements.

For the second type of tested TI interpolator assigning a quantization step to the TDL delays can be done in the same way as it has been done for the first type of interpolator. However, such an assignment for the third type of tested TI interpolator is usually done differently. Here, STOP signal *chases* START signal. The shortest and the longest distances between START and STOP signals determine which flip-flops are active and which ones are not. So in this case the best solution seems to be assigning the delay of the first active segment to the 0-th quantization step, assigning the delay of the second active segment to the 1-st quantization step, and so on. Please notice that the segment delay is here equal to the difference  $\tau_B - \tau_A$ . The first and the last active segments are usually used only partly, so statistically (the code-density test [2, 21, 23]) the measured sizes of these segments are usually smaller than this difference.

Three tested types of TI interpolators have different maximum intensities of interpolations. The first one (Fig. 1a) has the highest maximum intensity of interpolations. Here, PULSES signal can register the state of TDL independently of CLOCK signal. The maximum intensity of interpolation is limited only by the flip-flop propagation time. The maximum intensity of interpolation of the second tested TI interpolator (Fig. 1b) is limited by the CLOCK signal

D. Chaberski, R. Frankowski, et al.: COMPARISON OF INTERPOLATORS USED FOR TIME-INTERVAL...

period. In this case, if two rising edges appear in the same CLOCK signal period, the first result is overwritten by the second result. The third type of TI interpolator (Fig. 1c) has the lowest maximum intensity of interpolation, because it is limited by the total delay (the sum of all active segments delays) of the *slower* TDL.

It was found that, when the frequency of the clock that is passed through the TDL changes, the TDL segment delay value also changes. This is caused by the local semiconductor structure temperature changes. This effect has been noticed for TI interpolators implemented in FPGA and it is supposed that a very similar effect appears also in ASIC. The TDL segment delay of the first type of TI interpolator is independent of the PULSES signal frequency because the TDL is fed by CLOCK signal of a constant frequency. However, the characteristics of the second and the third TI interpolators depend on the PULSES signal frequency changes. This effect has been examined thoroughly by the authors and the test results are described in the next sections of this paper.

When m TI interpolators are used, then the number of measurements increases m times. A quantization step size of the measurement system that consists of m interpolators presented in Figs. 1a, 1b are inversely proportional to mn, where n is the number of TDL segments. However, when the measurement system consists of m TI interpolators presented in Fig. 1c, the quantization step is proportional merely to mn - n + 1. A deeper discussion about this feature is contained in Subsection 4.1.

To obtain a proper value of high-resolution quantisation step when m TI interpolators are used, one has to calculate relative time offsets between TDL inputs when two first types of interpolators are used (Figs. 1a, 1b) [17]. When the third type of TI interpolator is used (Fig. 1c) these time offsets influence the selection of the first active segment in each TDL and such calculations are needless [18].

Other types of TI interpolators can be found in [1–4, 20]. For example, in [20] the TDL delay elements have been created regarding the fact that the flip-flop propagation time  $t_{CQ}$  is limited. We have not tested this type of TI interpolator but we suspect that a similar influence of the intensity of registered pulses on the TDL characteristic would appear also for this solution.

# 3. Selected research topics

This section contains a description of some research issues that aim to complete the image of described research results. The following subsections describe the TI generator responsible for providing a double PULSES signal and the methods used for examining the influence of the intensity of an event on the TI interpolator characteristic as well as the dependency of the maximum intensity of registered events on the TI interpolator type. The last subsection describes some implementation details of tested TI interpolators.

# 3.1. TI generator

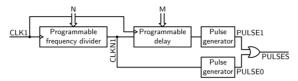

In order to compare TI interpolators the TI generator presented in Fig. 2 has been used. The programmable frequency divider generates a rising edge every N CLK1 signal periods (please refer also to Fig. 3). The programmable delay generates one CLK1 period-wide pulse after M clock cycles since the CLKN1 signal rising edge appeared. Both pulse generators unify a width of the pulses (PULSE0 and PULSE1) and finally both these pulses are connected by the OR function. The signal created in this way is then just provided to the TI interpolator PULSES input.

Fig. 2. A block diagram of the TI generator used for testing TI interpolators.

Fig. 3. A timing diagram of the TI generator presented in Fig. 2.

The programmable generator is cycled by the CLK1 clock that is non-synchronous with the standard-clock (CLK0) of TI interpolators. This feature enables to test every segment of TI interpolator. If these clocks were synchronous only a few selected segments would be tested.

The PULSES signal (Fig. 2) contains two TIs. The longer TI of a length (N-M)T enables to controllably test TI interpolator heating. The shortest TI of a length MT is measured by the TI interpolator and the result (TI histogram) determines whether the tested interpolator works properly or not.

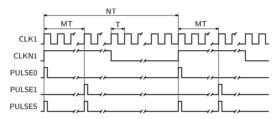

## 3.2. TI interpolator characteristic change observation method

It is generally known that the TDL characteristic depends on its temperature. For the XILINX Virtex5 FPGA structure a temperature increase causes an increase of the TDL segment delay. Fig. 4 shows an example of the dependence of TI interpolator characteristic on its temperature. Please notice (the heating case) that, when the temperature increases, all (0–5, 7) but one (6) of TI interpolator quantization steps also increase. The 6-th quantization step decreases because its value is calculated accordingly to (1). Its value is not equal to the corresponding TDL segment value as it happens for the remaining quantization steps.

When all, except one, TI interpolator quantization steps have the same trend of changes and this one TI interpolator quantization step depends on the sum of remaining TI quantization steps, then this one quantization step is the most sensitive to the temperature changes. The TI interpolator characteristic change observation method utilizes this fact. To obtain an average TDL segment delay value  $\langle q \rangle$ , the following formula is used:

$$\langle q \rangle = \frac{T - q_m}{n - 1} \,, \tag{2}$$

where T is a standard-clock period; n is the number of quantization steps and  $q_m$  is a quantization step given by (1).

In this paper not just the TDL segment delay dependence on ambient or average structure temperature has been examined, but also its dependence on the intensity of registered pulses. When the intensity of these pulses increases, the temperature of TDL also increases and finally the TDL segment delay increases, too.

D. Chaberski, R. Frankowski, et al.: COMPARISON OF INTERPOLATORS USED FOR TIME-INTERVAL...

Fig. 4. Demonstration of the dependence TI interpolator characteristic on the structure temperature change.

# 3.3. Test of TI interpolator maximum intensity

The maximum intensity of the interpolator has been tested by checking whether this interpolator is able to operate properly and measure faultlessly at the maximum (theoretically determined) intensity of pulses. If this test was passed, then it was checked whether this TI interpolator failed at a little bit higher frequency of pulses. If any of these two predictions had appeared to be wrong, the TI interpolator model would have to be corrected.

# 3.4. Some implementation details

All tested TI interpolators have been implemented in the XILINX Virtex5 XC5VLX50 FPGA structure. The mentioned FPGA structure enabled to implement either 125 of 32-segment interpolators presented in Figs. 1a, 1b, or 50 of 80-segment interpolators presented in Fig. 1c. For all TI interpolators a standard-clock period of 10 ns was used. The period of this clock fits the whole 32-segment TDL delay of the interpolator (Figs. 1a, 1b), so the average resolution is equal to about 312.5 ps for a single interpolator and to about 2.5 ps for all 125 interpolators. For the third TI interpolator (Fig. 1c) the number of quantization steps (the number of active TDL segments) was within a range from 66 to 69. From a practical point of view the number of quantization steps has been reduced to 64 by software. In this case the average resolution of a single TDL was equal to about 156.25 ps and the resolution obtained for all 50 TDLs was equal to about 3.125 ps.

To create TDL segments LUT elements have been used. The effective delay of a segment of TDL constructed with the use of LUTs strongly depends on the route of the connecting wire. This route depends mainly on the input of LUT that was used. To control a particular TDL segment delay one has only to choose a proper LUT input – in most cases this operation is sufficient. This control is easily available when the design is made with the use of the FPGA structure editor. When the design is described in *Very High Speed Integrated Circuit Hardware Description Language* (VHDL) a *User Constraint File* (UCF) can be used to limit the delay of the path. Even when the design uses LUT1 (one input LUT component) the implementation process uses one but can use any input of the LUT. When a TDL is created as a macro (\*.nmc file) then the situation is the same as when the TDL is described in VHDL.

# 4. Concept of multiple measurement

For every hit (Start, Stop or multi-Stop) a high-precision TS is obtained by finding the common part of all TSs generated by this hit and registered by all TDLs. Fig. 5a explains these operations when the total number of TDLs is equal to 4. Each TS is represented by its beginning and its ending. The resultant high-resolution TS beginning is equal to the maximum

value of all TS beginnings, and – analogously – the ending of the high-resolution TS is equal to the minimum value of all TS endings [17, 18, 24].

Please notice (Fig. 5a) that when the number (m) of TDLs increases, the high resolution TS is usually becoming narrower in this example (the resultant TS is better located). Finally, the beginning of the high resolution TS for Start is determined by the beginning of  $E_{2,i+1}$  TS, whereas its ending is determined by the ending of  $E_{3,i-1}$  TS. For the Stop hit the high resolution TS is equally precise for m=1 or m=2, but finally (m=4) it becomes narrower and is determined by the beginning of  $E_{3,i}$  TS and the ending of  $E_{2,i+1}$  TS.

Fig. 5. The concept of multiple-measurement time-interval PDF calculation; an example of obtaining high-precision time stamps from time stamps generated by four TDLs for two consecutive hits (a); time-interval PDFs obtained for two consecutive time-stamp pairs depending on the number m of used TDLs (b).

It is very convenient to determine TIs as *Probability Density Functions* (PDFs). Then, while constructing a TI histogram not just only one point is added to it, but the PDF of this TI is added and finally TI histograms are more accurate. These PDFs for TI can be calculated by the use of the *Quantization and Non-linearity Minimization* (QNM) method [24]. Fig. 5b explains obtaining PDFs for TS pairs (Start and Stop) in the case of multiple-measurement TDC. Here, the PDF is a modified convolution (the sign of the first argument has been changed) of high-resolution TSs obtained for Start and Stop events. When TSs for Start and Stop are narrower, then a TI can be determined more precisely and its PDF is higher and narrower (this is clearly visible in Fig. 5b).

Inaccuracy of calculation of the TDL offsets for TDCs based on both first interpolators (Figs. 1a, 1b) based on MTDL is the main source of TI calculation errors [17]. Every TS that depends on any quantization step of *j*-th TDL will be corrupted when *j*-th TDL offset is inappropriately pointed out. Before calculating a high-resolution TS one has to calculate this offsets.

## 4.1. Increase of resolution

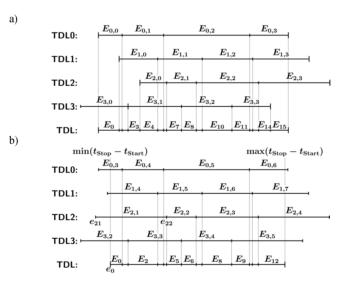

As mentioned in Section 2, an increase of resolution depends on the type of used TI interpolators. When TI interpolators of the type presented in Figs. 1a, 1b are used, then the resultant TI interpolator increases the measurement resolution mn times, but when the TI interpolator presented in Fig. 1c is used – the measurement resolution increases mn - n + 1 times, where m is the number of TI interpolators and n is the number of segments in each TDL. This difference is explained in Fig. 6.

Figure 6a shows the situation when each quantization step limit point of any TDL that is located within a reference TDL (TDL0) beginning and ending range creates a limit point in the resultant TDL. In this case the TDL number 0 provides n+1 limit points and any other TDL provides n limit points. The number of limit points is equal to mn+1 and the number of quantization steps is equal to mn.

When each limit point of any TDL that is located within a range of minimum  $\min(t_{Stop} - t_{Start})$  and maximum  $\max(t_{Stop} - t_{Start})$  difference between Stop and Start event appearance moments creates a limit point in the resultant TDL (Fig. 6b), then m(n-1) limit points are added to the resultant TDL. For this TI interpolator type 2 additional points:  $\min(t_{Stop} - t_{Start})$  and  $\max(t_{Stop} - t_{Start})$  have to be added to the resultant TDL. In this way, m(n-1)+2=mn-m+2 limit points have been added that creates mn-m+1 quantization steps.

Fig. 6. Explanation of the resolution increase mechanism for multiple TDL TDC; the resultant beginning and ending are determined by the TDL0 beginning and ending (a); the resultant beginning and ending are determined by the minimum and the maximum difference between Start and Stop pulses (b).

In this case no offset values between TDLs have to be calculated. Please notice (Fig. 6b) that here these offset values are just coded as the first active segment index and its utilization. For example, utilization of TDL2 first active segment ( $E_{2,1}$ ) is equal to  $\frac{e_{2,2}-e_0}{E_{2,1}}$ . When the delay value of TDL2 increases by (a little) more than  $e_0-e_{2,1}$  then  $E_{2,1}$  will be utilised totally, and  $E_{2,0}$  will become the first active segment.

## 5. Experimental results

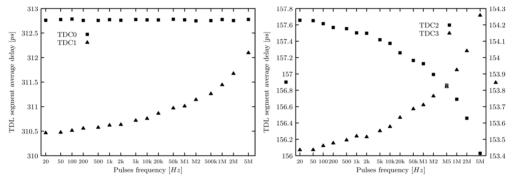

The experimental results mainly show the influence of registered pulses' frequency on the TI interpolator characteristic. Three types of interpolators (Figs. 1a, 1b, 1c) have been examined and the last type (Fig. 1c) of interpolator has been verified for two variants.

According to the expectations (Section 2), an average TDL segment delay does not depend on the pulses' frequency for the first type of TI interpolator (Fig. 7, TDC0) and the TDL segment delay increases when the pulses' frequency increases for the second type of TI interpolator (Fig. 7, TDC1).

The third type of tested interpolator consists of two TDLs. The first variant of this TI interpolator is based on the fact that the bottom TDL (Fig. 1c) has been connected permanently to the standard clock (100 MHz), so its characteristic does not depend on the pulses' frequency. However, the top TDL is connected to PULSES signal, so its characteristic depends on the pulses' frequency. For the second variant of this interpolator the bottom TDL is provided with the standard-clock cycle only when the pulse appeared, whereas the top TDL is connected to PULSES signal exactly in the same way as in the first variant of this interpolator type. Here, the segment values of both TDLs increase when the frequency of pulses increases.

Fig. 7. The dependence of the (single/double) TDL segment average delay on the intensity of registered PULSES.

Concluding, the average double TDL segment delay of the first variant of the third TI interpolator type decreases when the pulses' frequency increases (Fig. 7 TDC2), because the difference  $\tau_B - \tau_A$  (Fig. 1c) decreases ( $\tau_B$  is constant and  $\tau_A$  increases) when the frequency of pulses increases. The average double TDL segment delay of the second variant of this interpolator increases, because both  $\tau_B$  and  $\tau_A$  increase proportionally to their values and  $\tau_B > \tau_A$  (Fig. 7 TDC3).

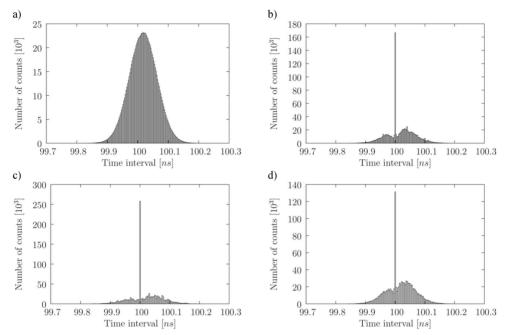

Figure 8 shows TI histograms between two pulses for every pair of pulses generated by the TI generator presented in Subsection 3.1. A nominal distance between pulses is equal to 10T, where  $T = 10 \, ns$  for all cases, so all histograms should be very similar, but they are not. One can see that the TI histogram presented in Fig. 8a is Gaussian, but the rest of them are more or less disturbed at a location of  $100 \, ns$ . The TI histograms presented in Fig. 8a are not disturbed, because this type TI interpolator characteristic (Fig. 1a) does not depend on the pulses' frequency. For all TI interpolators the characteristics were measured when a frequency of pairs of pulses was equal to 1 kHz. However, the TI histograms presented in Figs. 8b, 8c, 8d are disturbed because TDL(s) had different characteristic(s) during the TI measurements from those during the characteristics' measurements. These disturbances result from the fact that a lot of TSs have been registered into quantization steps that originally (1 kHz) were narrow (they

are now known as narrow ones) but after changing the frequency of pairs of pulses to 5 MHz these quantization steps became wider because of a particular TDL quantization step beginning and ending shift (Fig. 6 may be helpful in imagining this process). Statistically, a wider TDL quantization step counts more hits but the result is reported, accordingly to the original characteristic, with a higher weight (contributions to the TI histogram are higher and narrower). The real characteristic is unknown, the characteristic that is used for calculation of the TI histogram is the best approximation that we know. The TDL characteristics are the only parameters of TDC that have changed; they changed accordingly to Fig. 7.

Fig. 8. The TI histograms between two pulses in a pair of pulses measured by the TI interpolator presented in Fig. 1a, Fig. 1b, Fig. 1c, when the standard clock is permanently (c); conditionally connected to the bottom TDL (d); when the intensity of pulse pairs is equal to 5 MHz and calculated when the characteristic of the TI interpolator was measured when the frequency of pairs of pulses was equal to 1 kHz.

The authors also tested initially TDLs constructed of CARRY elements implemented in XILINX Virtex4 XC4VLX25. A similar influence of the pulses' frequency on the TDL segment delay has been noticed. However, for CARRY elements this influence was relatively a little bit smaller and was equal to about 70% of that noticed for LUT elements in a tested range from 500 Hz to 5 MHz of registered PULSES.

The maximum intensity of registered PULSES of the TI interpolator presented in Fig. 1a was equal to about  $4 \times 10^8$  pulses per second,  $5 \times 10^7$  for the interpolator shown in Fig. 1b, and only  $33 \times 10^6$  for both variants of the interpolator presented in Fig. 1c.

### 6. Conclusions

The experimental results and theoretical analyses have shown that the best type of interpolator for TI multi-measurement systems is that presented in Fig. 1a. The characteristic of interpolator of this type does not depend on the registered pulses' frequency, so when it is measured once (for one pulses' frequency), it can be used for calculating TI between pulses

of other frequencies without causing errors. The measured TI histograms presented in Fig. 8 clearly confirm this statement. The authors performed in-depth tests of TDLs made of LUT elements and initial tests of TDLs made of CARRY elements. For both types of TDLs these characteristic changes are observed.

However, using this type of interpolator to extend a measurement range either two counters, a Grey code counter or a mutually-complementing counter-register pair are required, but this hardware is needed only for one selected TI interpolator (the other interpolators just inherit this information). The only real difficulty of using TI interpolator of this type for multi-measurement systems is the need of calculating TDL offsets. Unfortunately, this operation requires a lot of measurements and demands a lot of computational time. Also, for this type of TI interpolator the largest measuring intensity is allowed. The maximum intensities of other interpolators are either limited by the standard-clock frequency or by the reverse of total TDL propagation time. Additionally, this one and the TI interpolators presented in Fig. 1b enable to obtain the highest ratio of resolution increase and the number of TDL segments.

The experimental results presented in this work show that for devices that use delay elements it is necessary to introduce an additional parameter that determines the frequency range within which either control or measurement can be carried out with a guaranteed precision.

To minimize the influence of pulses' frequency change on the TDL characteristic change one could use either a delay-locked or a phase-locked loop [20] for the TI interpolators presented in Figs. 1b, 1c. This loop can be created by implementation of a dummy delay element that is placed nearby the stabilised TDL, so that this delay is sensitive to the temperature of stabilised TDL and – what follows – is sensitive to the pulses' intensity.

#### References

- [1] Henzler, S. (2010). Time-to-Digital Converters. *Springer Series in Advanced Microelectronics*. 29, Springer Publishing Company, Incorporated.

- [2] Zieliński, M. (2009). Review of single-stage time-interval measurement modules implemented in FPGA devices. *Metrol. Meas. Syst.*, 16(4), 641–647.

- [3] Kalisz, J. (2004). Review of methods for time interval measurements with picosecond resolution. *Metrologia*, 41(1), 17–32.

- [4] Szplet, R. (2014). Time-to-Digital Converters. In Carbone, P., Kiaei, S., Xu, F. Design, Modeling and Testing of Data Converters. Springer Berlin Heidelrberg, 211–246.

- [5] Zieliński, M., Chaberski, D., Grzelak, S. (2003). Time-interval measuring modules with short deadtime. *Metrol. Meas. Syst.*, 10(3), 241–251.

- [6] Torres, J., Aguilar, A., Garcia-Olcina, R., Martinez, P., Martos, J., Soret, J., Benlloch, J., Conde, P., Gonzalez, A., Sanchez, F. (2014). Time-to-digital converter based on FPGA with multiple channel capability. *IEEE Trans. Nucl. Sci.*, 61(1) 107–114.

- [7] Song, J., An, Q., Liu, S. (2006). A high-resolution time-to-digital converter implemented in field-programmable-gate-arrays. *Nuclear Science, IEEE Transactions on*, 53(1), 236–241.

- [8] Mandai, S., Charbon, E. (2012). A 128-Channel, 8.9-ps LSB, Column-Parallel Two-Stage TDC Based on Time Difference Amplification for Time-Resolved Imaging. *Nuclear Science, IEEE Transactions on*, 59(5), 2463–2470.

- [9] Young-Hun, S., Jun-Seok, K., Hong-June, P., Jae-Yoon, S. (2012). A 1.25 ps Resolution 8b Cyclic TDC in 0.13 µm CMOS. Solid-State Circuits. *IEEE Journal*, 47(3), 736–743.

- [10] Jansson, J.P., Koskinen, V., Mäntyniemi, A., Kostamovaara, J. (2012). A Multichannel High-Precision CMOS Time-to-Digital Converter for Laser-Scanner-Based Perception Systems. *Instrumentation and Measurement, IEEE Transactions on*, 61(9), 2581–2590.

D. Chaberski, R. Frankowski, et al.: COMPARISON OF INTERPOLATORS USED FOR TIME-INTERVAL...

- [11] Fishburn, M., Menninga, L., Favi, C., Charbon, E. (2013). A 19.6 ps, FPGA-Based TDC With Multiple Channels for Open Source Applications. *Nuclear Science, IEEE Transactions on*, 60(3), 2203–2208.

- [12] Perktold, L., Christiansen, J. (2014). A multichannel time-to-digital converter ASIC with better than 3 ps RMS time resolution. *Journal of Instrumentation*, 9(1), C01060.

- [13] Wu, J., Shi, Z. (2008). The 10-ps wave union TDC: Improving FPGA TDC resolution beyond its cell delay. Nuclear Science Symposium Conference Record, 3440–3446.

- [14] Grzelak, S., Kowalski, M., Czoków, J., Zieliński, M. (2014). High resolution time-interval measurement systems applied to flow measurement. *Metrol. Meas. Syst.*, 21(1), 77–84.

- [15] Grzelak, S., Czoków, J., Kowalski, M., Zieliński, M. (2014). Ultrasonic flow measurement with high resolution. *Metrol. Meas. Syst.*, 21(2), 305–316.

- [16] Frankowski, R., Gurski, M., Płóciennik, P. (2016). Optical methods of the delay cells characteristics measurements and their applications. Opt. Quantum Electron., 48(3), 1–19.

- [17] Chaberski, D. (2016). Time-to-digital-converter based on multiple-tapped-delay-line. *Measurement*, 89, 87–96.

- [18] Szplet, R., Jachna, Z., Kwiatkowski, P., Różyc, K. (2013). A 2.9 ps equivalent resolution interpolating time counter based on multiple independent coding lines. *Measurement Science and Technology*, 24(3), 1–15.

- [19] Zieliński, M., Chaberski, D., Kowalski, M., Frankowski, R., Grzelak, S. (2004). High-resolution timeinterval measuring system implemented in single FPGA device. *Measurement*, 35(3), 311–317.

- [20] Rahkonen, T., Kostamovaara, J. (1993). The Use of Stabilized CMOS Delay Lines for the Digitization of Short Time Intervals. IEEE Journal of Solid-State Circuits, 28(8), 887–894.

- [21] Frankowski, R., Chaberski, D., Kowalski, M. (2015). An optical method for the time-to-digital converters characterization. *Proc. IEEE ICTON 2015*, Budapest, Hungary, We.P.14, 1–4.

- [22] Wu, J. (2010). Several key issues on implementing delay line based TDCs using FPGAs. Nuclear Science, IEEE Transaction on, 57(3), 1543–1548.

- [23] Frankowski, R., Zieliński, M. (2015). A sub-channel method for the time-intervals histogram calculation. Proc. IEEE ICTON 2015, Budapest, Hungary, We.P.14, 1–5.

- [24] Chaberski, D., Zieliński, M., Grzelak, S. (2009). The new method of calculation sum and difference histogram for quantized data. *Measurement*, 42(9), 1388–1394.