METROLOGY AND MEASUREMENT SYSTEMS

Index 330930, ISSN 0860-8229 www.metrology.wat.edu.pl

# DESIGN OF NEW ROBUST BACKSTEPPING CONTROL FOR THREE-PHASE GRID-CONNECTED FOUR-LEG SOURCE VOLTAGE PWM CONVERTERS

# Ali Chebabhi<sup>1)</sup>, Abdelhalim Kessal<sup>2)</sup>

1) Electrical Engineering Laboratory (EEL), Faculty of Technology, University of M'sila, M'sila 28000, Algeria (ali.chebabhi@univ-msila.dz)

2) LPMRN Laboratory, Faculty of Sciences and Technology, University of Bordj Bou Arreridj, 34000, Algeria (⊠ abdelhalim.kessal@univ-bba.dz)

#### Abstract

Due to high performance demands of grid-connected pulse-width modulation (PWM) converters in power applications, backstepping control (BSC) has drawn wide research interest for its advantages, including high robustness against parametric variations and external disturbances. In order to guarantee these advantages while providing high static and dynamic responses, in this work, a robust BSC (RBSC) with consideration of grid-connected PWM converter parameter uncertainties is proposed for three-phase grid-connected four-leg voltage source rectifiers (GC-FLVSR). The proposed RBSC for GC-FLVSR is composed of four independent controllers based on the Lyabonov theory that control DC bus voltage and input currents simultaneously. As a result, unit power factor, stable DC-bus voltage, sinusoidal four-leg rectifier input currents with lower harmonics and zero-sequence (ZS), and natural currents can be accurately achieved. Furthermore, the stability and robustness against load, DC capacitor, and filter inductance variations can be tested. The effectiveness and superiority of the proposed RBSC compared to the PI control (PIC) have been validated by processor-in-the-loop (PIL) co-simulation using the STM32F407 discovery-development-board as an experimental study.

Keywords: three-phase grid-connected four-leg voltage source rectifiers (GC-FLVSR), Robust Backstepping Control (RBSC), parameters uncertainties, harmonic, Zero Sequence Currents (ZSCs), Unit Power Factor (UPF).

© 2023 Polish Academy of Sciences. All rights reserved

# 1. Introduction

In recent decades, three-phase grid-connected three-leg voltage source rectifiers have been widely used in numerous industrial power applications, such as grid power factor correction, *doubly fed induction generator* (DFIG)-based wind energy systems feeding stand-alone loads, *high-voltage-direct-current* (HVDC) systems, and *electric vehicle* (EV) charging systems [1–3]. They are considered a high-merit system for high-power applications due to their excellent input current quality, *unit power factor* (UPF), controllable DC-bus voltage, and bidirectional power

Copyright © 2023. The Author(s). This is an open-access article distributed under the terms of the Creative Commons Attribution-NonCommercial-NoDerivatives License (CC BY-NC-ND 4.0 https://creativecommons.org/licenses/by-nc-nd/4.0/), which permits use, distribution, and reproduction in any medium, provided that the article is properly cited, the use is non-commercial, and no modifications or adaptations are made.

Article history: received August 6, 2022; revised September 26, 2022; accepted November 30, 2022; available online January 23, 2023.

www.czasopisma.pan.pl

A. Chebabhi, A. Kessal: DESIGN OF NEW ROBUST BACKSTEPPING CONTROL...

flow. However, for several other industrial power applications, the traditional three-leg PWM rectifier may not be an exemplary solution due to the unbalanced single-phase nonlinear loads or the unbalanced grid voltage and asymmetrical impedance [4, 5].

To solve these issues, the utilization of *four-leg PWM voltage source rectifiers* (FLVSR) is highly recommended. These PWM converters are appropriate to maintain balanced sinusoidal grid currents and voltages under all unbalanced conditions and other disturbances [6, 7]. The fourth leg, inserted into the traditional PWM rectifier, provides a *zero-sequence current* (ZSC) path and control and preserves the capability to handle all unbalanced issues [8]. Four-leg PWM converters have commonly been used in stand-alone power generation systems [7], active power filters [9], and distributed static compensators [10].

The control performance and dynamic responses of *grid-connected four-leg voltage source rectifiers* (GC-FLVSR) are strongly dependent on the selected outer DC-bus voltage and inner three-input current controllers. The several controllers that have been developed and used for four-leg converters have the same targets with diverse functionalities [11]. Linear *proportional integral controllers* (PICs) have been proposed to obtain good steady-state performance [12]. However, the ingrained nonlinearities of these four-leg converters and the undesirable disturbances due to parameter changes not only affect the control performance of the PIC [13], but also cause poor dynamic responses in transient-states.

In recent years, several nonlinear techniques have been proposed to improve the control performance and dynamic responses of PWM converters, including *state-space current control* (SSCC) [5], *flatness control* (FC) [13], *sliding mode control* (SMC) [14], *fast terminal sliding mode control* (FTSMC) [15], and *backstepping control* (BSC) [16].

Among the above-mentioned techniques, the classical BSC has been known as an effective and successful technique due to its features of systematic, recursive design, robustness, and better performance under diverse operating conditions. The concept of the classical BSC is to select suitable Lyapunov functions according to the control purposes of all steps of the overall control system [9, 16]. These functions can guarantee the stability and robustness of the control system. Thus, the BSC technique was applied to a three-leg PWM rectifier with the function of controlling both the instantaneous power and DC-bus voltage simultaneously. In [17–19], simulations and experimental results demonstrated that the classical BSC is efficient in terms of stability, robustness, harmonic elimination, disturbance rejection, and power factor correction. A review of the features of BSC in PWM converters is presented in [20]. However, the three-leg converter is still considered the essential converter in the aforementioned works based on the BSC technique. Consequently, the ZSC generated in the case of unbalanced single-phase loads and grid voltages is not considered, and the PWM converter parameter uncertainties are not taken into account in the theoretical framework of the classical BSC technique, so control system robustness cannot be guaranteed.

In this paper, a *robust backstepping control* (RBSC) technique with consideration of GC-FLVSR uncertainties is proposed to control the DC-bus voltage and input currents of GC-FLVSR in the dq0 frame under diverse operating conditions such as DC-bus voltage change, load change, and parameter variations. The four-leg PWM rectifier is adopted here for its capacity to provide a ZSC path and regulation and thus avoid grid voltage fluctuation. In this paper, the transient and steady state control performances of the proposed RBSC are evaluated and compared with those based on the traditional PIC in terms of reference tracking, integral performance, DC-bus voltage stabilization, input current harmonic and ZSC eliminations, power factor correction, and neutral current mitigation. The proposed RBSC technique provides favourable and satisfactory results for all previous control performance indicators that confirm the superiority and effectiveness of the proposed control strategy.

The rest of this paper is organized as follows: in Section 2, the dynamic model of the 3P-4LR is presented. Then, detailed DC-bus voltage and input current control loops based on the proposed RBSC technique are developed and detailed in Section 3. Section 4 presents the PIL co-simulation results and discusses the viability and effectiveness of the proposed RBSC technique for 3P-4LR. Finally, Section 5 summarizes the contributions of this work.

## 2. Modelling of three-phase GC-FLVSR

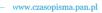

The three-phase FLVSR connected to the grid through filter inductors  $(L_{f abcn})$  with parasitic resistances  $(R_{f abcn})$  is shown in Fig. 1. The grid is presented by three sinusoidal voltages  $(e_{abc})$  and a grid neutral line in series with four inductors  $(L_{gabcn})$  that have internal resistances  $(R_{gabcn})$  and are connected with the load through the DC capacitor  $(C_{dc})$ . The grid currents, input currents, and input voltages are  $i_{gabcn}$ ,  $i_{f abcn}$ , and  $v_{f abcn}$  respectively.  $I_L$ ,  $I_c$ ,  $I_{dc}$ , and  $V_{dc}$  are the load current, capacitor current, DC current, and DC voltage, respectively.

Fig. 1. Structure of the three-phase grid-connected four-leg voltage source rectifier (GC-FLVSR).

To facilitate the controller design, the model of FLVSR is given in dq0 frame [13] as:

$$\frac{di_{fd}}{dt} = -\frac{R_f}{L_f} i_{fd} + \omega i_{fq} - \frac{v_{gd}}{L_f} + \frac{v_{fd}}{L_f} \\

\frac{di_{fq}}{dt} = -\frac{R_f}{L_f} i_{fq} - \omega i_{fd} - \frac{v_{gq}}{L_f} + \frac{v_{fq}}{L_f} \\

\frac{di_{f0}}{dt} = -\frac{(R_f + 3L_n)}{(L_f + 3L_n)} i_{f0} - \frac{v_{g0}}{(L_f + 3L_n)} + \frac{v_{f0}}{(L_f + 3L_n)},$$

(1)

where:  $i_{f dq0}$  and  $v_{f dq0}$  are the active, reactive, and ZS input currents and voltages, respectively.  $\omega$  is the grid angular frequency. According to (1), there are coupling terms between  $i_{f d}$  and  $i_{f q}$ .

A. Chebabhi, A. Kessal: DESIGN OF NEW ROBUST BACKSTEPPING CONTROL...

These terms are mitigated by introducing the decoupling variables  $u_d$  and  $u_q$  as follows:

$$\underbrace{u_d}_{\text{feedback}} = -\left(L_f \frac{\text{d}i_{fd}}{\text{d}t} + R_f i_{fd}\right)$$

$$\underbrace{u_q}_{\text{feedback}} = -\left(L_f \frac{\text{d}i_{fq}}{\text{d}t} + R_f i_{fq}\right)$$

$$\underbrace{u_0 = -\left((L_f + 3L_n)\frac{\text{d}i_{f0}}{\text{d}t} + (R_f + 3R_n)i_{f0}\right)$$

$$u_{dc} = i_{fd} = \frac{C}{2V_{gd}}\left(\frac{\text{d}V_{dc}^2}{\text{d}t} + \frac{2V_{dc}^2}{CR_L}\right)$$

(2)

The FLVSR input voltages or the control input variables  $v_{f dq0}^*$  in the dq0 frame are given as:

$$\left(\begin{array}{c}

\underbrace{v_{fd}^{*}}_{\text{feedback}} = u_{d} + \underbrace{\omega L_{f} i_{fq} + V_{g \max}}_{\text{feedforward}} \\

\underbrace{v_{fq}^{*}}_{\text{feedback}} = u_{q} - \underbrace{\omega L_{f} i_{fd}}_{\text{feedforward}} \\

\underbrace{v_{fq}^{*}}_{\text{feedback}} = u_{0} \\

i_{fd}^{*} = u_{dc}

\end{array}\right).$$

(3)

From (1), it is clear that the ideal GC-FLVSR when the uncertainties are not considered consists of four dynamic models, DC voltage and three input currents. In the next section, we are rearranging these dynamic models for the case when the uncertainties were considered as bellow.

## 2.1. Dynamic model of DC bus voltage and active input current

From (1), the square DC voltage dynamic, considering its uncertainty, can be expressed as:

$$\frac{dV_{dc}^2}{dt} = a_{dc}V_{dc}^2 + b_{dc}u_{dc}$$

$$= (a_{dc} + \Delta a_{dc})V_{dc}^2 + (b_{dc} + \Delta b_{dc})u_{dc}, \qquad (4)$$

$$= a_{dc}V_{dc}^2 + b_{dc}u_{dc} + \psi_{dc}(t)$$

$$\psi(t) = \Delta a_{dcn}V_{dc}^2 + \Delta b_{dcn}u_{dc}$$

where:  $a_{dc} = -\frac{2}{C_{dc}Z_L}$ ,  $b_{dc} = \frac{2v_{g \max}}{C_{dc}}$ .  $a_{dcn}$  and  $b_{dcn}$  are the nominal values of  $a_{dc}$  and  $b_{dc}$ , respectively.  $\Delta a_{dcn}$  and  $\Delta b_{dcn}$  are the parameter variations.  $\psi_{dc}(t)$  is the DC bus voltage dynamic model uncertainty function, whose limit value is given as  $|\psi_{dc}(t)| < \delta_{dc}$ .

When the active input current dynamic uncertainty is considered, (1-a) can be rewritten as:

$$\frac{di_{fd}(t)}{dt} = a_d i_{fd}(t) + b_d u_d(t)

= (a_{dn} + \Delta a_{dn}) i_{fd}(t) + (b_{dn} + \Delta b_{dn}) u_d(t) ,$$

$$= a_{dn} i_{fd}(t) + b_{dn} u_d(t) + \psi_d(t)

\psi_d(t) = \Delta a_{dn} i_{fd}(t) + \Delta b_{dn} u_d(t)$$

(5)

where:  $a_d = -\frac{R_f}{L_f}$ ,  $b_d = -\frac{1}{L_f}$ .  $a_{dn}$  and  $b_{dn}$  are the nominal values of  $a_d$  and  $b_d$  respectively.  $\psi_d(t)$  is the active input current dynamic uncertainty function whose limit value is supposed to be given as  $|\psi_d(t)| < \delta_d$ .

# 2.2. Dynamic model of reactive input current

When the reactive input current dynamic uncertainty is considered, (1-b) can be rewritten as:

$$\frac{di_{fq}(t)}{dt} = a_q i_{fq}(t) + b_q u_q(t)

= (a_{qn} + \Delta a_{qn}) i_{fq}(t) + (b_{qn} + \Delta b_{qn}) u_q(t) , \qquad (6)

= a_{qn} i_{fq}(t) + b_{qn} u_q(t) + \psi_q(t)

\psi_q(t) = \Delta a_{qn} i_{fq}(t) + \Delta b_{qn} u_q(t)$$

where:  $a_q = -\frac{R_f}{L_f}$ ,  $b_q = -\frac{1}{L_f}$ .  $a_{qn}$  and  $b_{qn}$  are the nominal values of  $a_q$  and  $b_q$  respectively.  $\psi_q(t)$  is the reactive input current dynamic uncertainty function whose limit value is supposed to be given as  $|\psi_q(t)| < \delta_q$ .

## 2.3. Dynamic model of zero sequence input current

When the ZSC dynamic uncertainty is considered, (1-c) becomes:

$$\frac{di_{f0}(t)}{dt} = a_0 i_{f0}(t) + b_0 u_0(t)

= (a_{0n} + \Delta a_{0n}) i_{f0}(t) + (b_{0n} + \Delta b_{0n}) u_0(t) ,$$

$$= a_{0n} i_{f0}(t) + b_{0n} u_0(t) + \psi_0(t)

\psi_0(t) = \Delta a_{0n} i_{f0}(t) + \Delta b_{0n} u_0(t)$$

(7)

where:  $a_0 = -\frac{(R_f - 3R_n)}{(L_f - 3L_n)}$ ,  $b_0 = -\frac{1}{(L_f - 3L_n)}$ ,  $a_{0n}$ , and  $b_{0n}$  are the nominal values of  $a_0$  and  $b_0$ respectively.  $\psi_0(t)$  is the ZSC dynamic uncertainty function whose limit is given as  $|\psi_0(t)| < \delta_0$ and  $\delta_{dc}$ ,  $\delta_d$ ,  $\delta_q$ , and  $\delta_0$  are positive constants.

## 3. Proposed RBSC technique for GC-FLVSR

## 3.1. RBSC for DC-bus voltage and active input current

By controlling the DC-bus voltage and active input current, two main objectives are addressed. One is to force the square of  $V_{dc}$  ( $V_{dc}^2 = x_v$ ) to track its reference ( $V_{dc}^{*2} = x_v^*$ ) and to provide

A. Chebabhi, A. Kessal: DESIGN OF NEW ROBUST BACKSTEPPING CONTROL ...

the active input current reference  $(i_{fd}^*)$  used in the active input current control loop. The other objective is to force the active input current  $i_{fd}$  to track its reference with zero steady state error to obtain the active input voltage reference  $v_{fd}^*$ .

The DC-bus voltage error is defined as  $e_v = x_v - x_v^*$ , and its derivative  $\dot{e}_v$  can be expressed as:

$$\dot{e}_{v} = \dot{x}_{v} - \dot{x}_{v}^{*}.$$

(8)

In order to enforce the DC-bus voltage error  $e_v$  to converge to zero asymptotically, a Lyapunov function defined as  $V_v = \frac{1}{2}e_v^2$  is selected and its derivative is expressed as:

$$\dot{V}_{v} = e_{v}(\dot{x}_{v} - \dot{x}_{v}^{*}).$$

<sup>(9)</sup>

Substituting  $\dot{x}_v$  from (4) into (9) results in:

$$\dot{V}_{v} = e_{v} \left( a_{dc} x_{v} + b_{dc} u_{dc} + \psi_{dc}(t) - \dot{x}_{v}^{*} \right).$$

(10)

The stability of  $V_{dc}$  control loop is ensured when the derivative of  $V_v$  given in (9) is strictly negative definite. For this, the term  $(a_{dc}x_v + b_{dc}u_{dc} + \psi_{dc}(t) - \dot{x}_v^*)$  can be expressed as [19]:

$$\left(a_{dc}x_{v} + b_{dc}u_{dc} + \psi_{dc}(t) - \dot{x}_{v}^{*}\right) = -k_{dc}e_{v} - \delta_{v}\operatorname{sgn}(e_{v}) + \psi_{dc}(t).$$

(11)

The derivative of Lyapunov function  $\dot{V}_{\nu}$  given in (10) becomes:

$$\dot{V}_{v} = -k_{dc}e_{v}^{2} - e_{v}\left(\delta_{v}\operatorname{sgn}\left(e_{v}\right) - \psi_{dc}(t)\right).$$

(12)

From (12),  $\dot{V}_v$  is strictly negative when  $\delta_v > |\psi_{dc}(t)|$  is satisfied.

As can be observed,  $\dot{V}_v$  will be strictly negative as long as  $\delta_v > |\psi_{dc}|$ , which confirms that the  $e_v$  will converge to zero and the stability of  $V_{dc}$  control loop can be guaranteed.

From (12), the control variable  $u_{dc} = i_{fd}^*$  of the  $V_{dc}$  control loop can written as follows:

$$i_{fd}^{*} = u_{dc} = \frac{1}{b_{dc}} \left( -k_{\nu} e_{\nu} - a_{dc} x_{\nu} - \delta_{\nu} \operatorname{sgn}(e_{\nu}) + \dot{x}_{\nu}^{*} \right).$$

(13)

In the active input current control loop, the term  $x_d = i_{fd}$  can be used as a state variable and  $u_d(t)$  as a decoupling variable. For this, the derivative of  $e_d = x_d - x_d^*$  is expressed as:

$$\dot{e}_d = \dot{x}_d - \dot{x}_d^* = \dot{x}_d - \dot{x}_d^*. \tag{14}$$

In order to enforce the tracking error  $e_d$  to zero asymptotically, the corresponding Lyapunov function is defined as  $V_d = \frac{1}{2}e_d^2$ , and its derivative can be expressed as:

$$\dot{V}_d = e_d \left( \dot{x}_d - \dot{x}_d^* \right). \tag{15}$$

Substituting  $\dot{x}_d$  from (5) into (15) results in:

$$\dot{V}_d = e_d(a_{dn}i_{fd}(t) + b_{dn}u_d(t) + \psi_d(t) - \dot{x}_d^*).$$

(16)

To guarantee the stability of the active input current control loop under the parameter uncertainties, the term  $(a_{dn}i_{fd}(t) + b_{dn}u_d(t) + \psi_d(t) - \dot{x}_d^*)$  in (16) must be expressed as:

$$a_{dn}i_{fd}(t) + b_{dn}u_d(t) + \psi_d(t) - \dot{x}_d^* = -k_d e_d - \delta_d \text{sgn}(e_d) + \psi_d(t).$$

(17)

By substituting (17) into (16), (16) becomes:

$$\dot{V}_d = -k_d e_d^2 - e_d (\delta_d \operatorname{sgn} (e_d) - \psi_d(t)).$$

(18)

According to (18),  $\dot{V}_d$  is strictly negative when  $\delta_d > |\psi_d(t)|$  is satisfied. According to (17), the decoupling control variable  $u_d$  is expressed as:

$$u_d(t) = \frac{1}{b_{dn}} (-a_{dn} x_d - k_d e_d - \delta_d \operatorname{sgn}(e_d) + \dot{x}_d^*).$$

(19)

By using (1-a), the active input reference voltage  $v_{fd}^*$  can be expressed as:

$$v_{fd}^* = \frac{1}{b_{dn}} (-a_{dn} x_d - k_d e_d - \delta_d \text{sgn}(e_d) + \dot{x}_d^*) + L_f \omega x_q + v_{gd}.$$

(20)

#### 3.2. BSC for reactive input current

The objective of this subsystem is to force the reactive input current error  $(e_q = x_q - x_q^*)$  to zero to provide a high power factor under reactive input current dynamic model uncertainties. The derivative  $\dot{e}_q$  of this tracking error is expressed as:

$$\dot{e}_q = \dot{x}_q - \dot{x}_q^*. \tag{21}$$

In order to enforce  $e_q$  to zero,  $V_q$  is defined as  $V_q = \frac{1}{2}e_q^2$ , and its derivative is thus written as:

$$\dot{V}_q = e_q (\dot{x}_q - \dot{x}_q^*).$$

(22)

Substituting  $\dot{x}_q$  from (6) into (22), it results in:

$$\dot{V}_q = e_q (a_{qn} x_q + b_{nq} u_q - \dot{x}_q^* + \psi_q(t)).$$

(23)

To guarantee that  $\dot{V}_q < 0$ , the term  $(a_{qn}x_q + b_{nq}u_q - \dot{x}_q^* + \psi_q(t))$  must be expressed as:

$$a_{qn}x_q + b_{qn}u_q(t) - \dot{x}_q^* + \psi_q(t) = -k_q e_q - \delta_q \text{sgn}(e_q) + \psi_q(t).$$

(24)

By substituting (24) into (23), (23) becomes:

$$\dot{V}_q = -k_q e_q^2 - \delta_q e_q \operatorname{sgn}(e_q) + e_q \psi_q(t).$$

<sup>(25)</sup>

This derivative is strictly negative when  $\delta_q > |\psi_q|$  is satisfied. From (25), the decoupling control variable  $u_q$  is given as follows:

$$u_{q} = \frac{1}{b_{qn}} (-a_{qn} x_{q} - k_{q} e_{q} - \delta_{q} \operatorname{sgn}(e_{q})),$$

(26)

$$v_{fq}^{*} = \frac{1}{b_{qn}} (-a_{qn} x_q - k_q e_q - \delta_q \operatorname{sgn}(e_q)) - \omega L_f i_{fd} + v_{gq}.$$

(27)

71

A. Chebabhi, A. Kessal: DESIGN OF NEW ROBUST BACKSTEPPING CONTROL ...

# 3.3. BSC for zero sequence input current

The objective of this subsystem is to force the ZSC ( $x_0 = i_{f0}$ ) to tend to zero with zero transient and steady state errors to mitigate the neutral current oscillation. The error of this current is defined as  $e_0 = x_0 - x_0^*$ , and its derivative is expressed as:

$$\dot{e}_0 = \dot{x}_0 - \dot{x}_0^*. \tag{28}$$

The Lyapunov function  $V_0$  is defined as  $V_0 = \frac{1}{2}e_0^2$ , and its derivative can be expressed as:

$$\dot{V}_0 = e_0 \dot{e}_0,$$

(29)

$$\dot{V}_0 = e_0(a_{0n}x_0 + b_{n0}u_0 + \psi_0(t)).$$

(30)

To guarantee the stability of this loop,  $(a_{0n}x_0 + b_{n0}u_0 + \psi_0(t))$  must be expressed as:

$$a_{0n}x_0 + b_{n0}u_0 + \psi_0 = -k_0e_0 - \delta_0\operatorname{sgn}(e_0) + \psi_0(t), \tag{31}$$

where,  $k_V$ ,  $k_d$ ,  $k_q$ , and  $k_0$  are positive constants.

By substituting (31) into (30), (30) becomes:

$$\dot{V}_0 = -k_0 e_0^2 - \delta_0 e_0 \operatorname{sgn}(e_0) + e_0 \psi_0(t).$$

(32)

This derivative is strictly negative when  $\delta_0 > |\psi_0|$  is satisfied.

From (31), the decoupling control variable of this control loop  $u_0$  is given as follows:

$$u_0 = \frac{1}{b_{n0}} (-a_{0n} x_0 - k_0 e_0 - \delta_0 \text{sgn}(e_0)), \tag{33}$$

$$v_{f\,0}^* = \frac{1}{b_{n0}} (-a_{0n} x_0 - k_0 e_0 - \delta_0 \text{sgn}(e_0)) + v_{g0}.$$

(34)

The advantages of the proposed RBSC over other traditional BSC are explained as follows:

The roles of the terms  $-k_v e_v$  in (13),  $-k_d e_d$  in (20),  $-k_q e_q$  in (27) and  $-k_0 e_0$  in (34) are useful to minimize the chattering phenomena in the proposed RBSC efforts because the terms  $-k_v e_v^2$  in (12),  $-k_d e_d^2$  in (19),  $-k_q e_q^2$  in (26) and  $-k_0 e_0^2$  in (33) will guarantee the negative value of the  $\dot{V}_v < 0$  and  $\dot{V}_{dq0} < 0$  even in the worst cases when  $\delta_v < |\psi_v(t)|, \delta_d < |\psi_d(t)|,$  $\delta_q < |\psi_q(t)|$  and  $\delta_0 < |\psi_0(t)|$ . On the other hand,  $\delta_{vdq0}$  can be accurately and conservatively chosen to avert the increase in the chattering phenomenon resulting from the terms  $\delta_v \operatorname{sgn}(e_v)$  in (12),  $\delta_d \operatorname{sgn}(e_d)$  in (19),  $\delta_q \operatorname{sgn}(e_q)$  in (26) and  $\delta_0 \operatorname{sgn}(e_0)$  in (33).

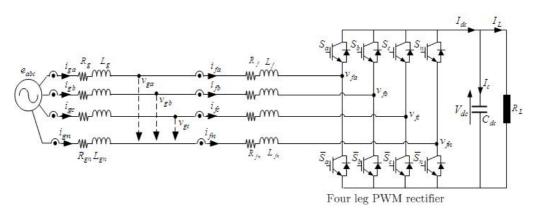

The proposed RBSC for GC-FLVSR is illustrated in Fig. 2. As it is shown, the input voltage references are provided by the inner loop controllers, and the outer loop controller is used to preserve a constant DC-bus voltage and provide a suitable active input current reference  $(x_d^* = i_{fd}^*)$ . The 3D-SVPWM method described in [9, 10] is applied in this work because of its significant advantages of constant switching frequency, low input voltage and current harmonics, high DC-bus voltage utilization, and low DC-bus voltage ripple.

Metrol. Meas. Syst., Vol. 30 (2023), No. 1, pp. 65–82 DOI: 10.24425/mms.2023.144399

Fig. 2. Proposed RBSC schematic of a three phase grid-connected four-leg voltage source rectifier.

# 4. Processor-in-the-Loop (PIL) co-simulation and performance evaluation of the proposed control strategy

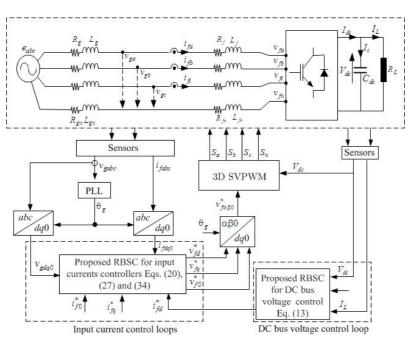

In order to validate the viability, performance, and effectiveness of the proposed RBSC for GC-FLVSR under parameter uncertainties, a PIL co-simulation of the system has been performed using an STM32F407 discovery-development-board in an experimental study based on the Euler method with a sample period of  $10^{-6}$ s using PowerGUI in the Simulink model. The co-simulation scenario studies were conducted for the proposed RBSC strategy to study two aspects: a) the effects of the proposed RBSC on response time, reactive power compensation, harmonics and ZSC mitigations, and DC voltage regulation; and b) the robustness and stability of the proposed RBSC under the variations of DC bus voltage, load, DC capacity, and filter inductors. The system and simulation parameters are given in Table 1.

Some PIL co-simulation results of the proposed RBSC and the PIC are provided for comparison. In addition, the errors of the DC-bus voltage and input currents are also represented and analysed in terms of performance integral criteria such as *Integral-Time-Absolute-Error* (ITAE) and *Integral-Time-Square-Error* (ITSE) [21]. These error performance indexes of the control outputs x ( $V_{dc}$ ,  $i_{fd}$ ,  $i_{fq}$  and  $i_{f0}$ ) and their references  $x^*$  are defined as:

$$\begin{cases} \text{ITAE} = \int_{0}^{t} t |x - x^{*}| dt \\ 0 & . \\ \text{ITSE} = \int_{0}^{t} t (x - x^{*})^{2} dt \end{cases}$$

(35)

A. Chebabhi, A. Kessal: DESIGN OF NEW ROBUST BACKSTEPPING CONTROL...

| Parameter                                 | Value              |  |

|-------------------------------------------|--------------------|--|

| AC grid voltage                           | 220 V              |  |

| Fundamental frequency of grid voltage     | 50 Hz              |  |

| DC-bus voltage $V_{dc}$                   | 700 V              |  |

| Capacitor of DC side rectifier $C_{dc}$   | 3 mF               |  |

| DC load resistance $R_L$                  | 100 Ω              |  |

| Input filter inductances $L_f$ , $L_{fn}$ | 2 mH, 1 mH         |  |

| Input filter resistances $R_f$ , $R_{fn}$ | 0.15 Ω             |  |

| Grid inductances $L_g$ , $L_{gn}$         | 0.1 mH, 0.05 mH    |  |

| Grid resistances $R_g$ , $R_{gn}$         | 0.1 Ω              |  |

| Sampling period of simulation             | 10 <sup>-6</sup> s |  |

| Switching frequency $f_s$                 | 16 kHz             |  |

Table 1. Values of system and co-simulation parameters.

The microcontroller of this discovery-development-board is the STM32F407VG, which features 1 Mb of flash memory, ARM®-Cortex®-M4F-CPU 32-bit architecture, *Floating Point Unit* (FPU), *Digital-Signal-Processor* (DSP), and 192KB SRAM with a maximum operational frequency of 168 MHz [22]. In Fig. 3, the proposed control technique for GC-FLVSR employing the STM32F407 discovery-development board is shown with its PIL structure.

Fig. 3. PIL co-simulation of the proposed RBSC-based grid-connected four-leg voltage source rectifier.

The implementation of the proposed control strategy for GC-FLVSR is carried out by consolidating all sub-control algorithms into a new single control circuit and defining the used microcontroller discovery-development-board in the system simulation as well as the inputs/outputs of the control circuit in MATLAB/Simulink. The algorithms in the control circuit are converted into C code using the embedded coder installed from MathWorks on the host PC that contains the Simulink model which, in turn, is uploaded into the STM32F407 development-board for flashing the compiled proposed control strategy to the microcontroller using a serial connection interface (YP-05 FTDI F232RL adapter) as shown in Fig 3. We integrate the previously generated C code in the PIL block into a new Simulink model to run the proposed control strategy on the STM32F407 development board [22]. After that, to control the system, the microcontroller computes the GC-FLVSR's state vectors and sends them to the host PC, which controls the Simulink power circuit of the GC-FLVSR via the same serial connection interface for operating it (Fig. 3).

# 4.1. Test 1 – Ideal operating conditions

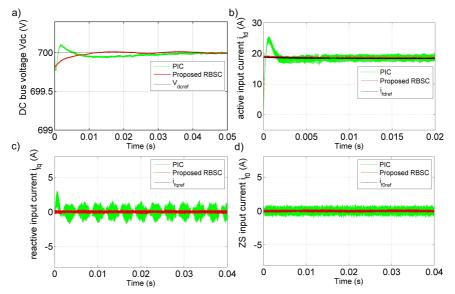

The comparative study of control performances of both controllers (PIC and proposed RBSC) was first carried out under ideal conditions and nominal values of the DC capacitor and filter inductors, as depicted in Figs. 4 (a to d). The integral error performance indexes (ITAE and ITSE) values for each controller were analysed and illustrated in Table 2. Also, the FLVSR dynamic responses for both strategies are represented in Figs. 4(a and b).

|      | Errors | PIC                   | Proposed RBSC         |

|------|--------|-----------------------|-----------------------|

| ITAE | $e_v$  | $3.925 \cdot 10^{-4}$ | $8.415 \cdot 10^{-5}$ |

|      | ed     | $8.914 \cdot 10^{-3}$ | $1.520 \cdot 10^{-3}$ |

|      | $e_q$  | $5.265 \cdot 10^{-3}$ | $1.141 \cdot 10^{-3}$ |

|      | $e_0$  | $3.734 \cdot 10^{-3}$ | $1.003 \cdot 10^{-3}$ |

| ITSE | $e_v$  | $3.275 \cdot 10^{-5}$ | $4.354 \cdot 10^{-7}$ |

|      | ed     | $6.864 \cdot 10^{-3}$ | $1.281 \cdot 10^{-3}$ |

|      | eq     | $4.931 \cdot 10^{-3}$ | $1.902\cdot 10^{-4}$  |

|      | $e_0$  | $3.503 \cdot 10^{-3}$ | $3.301 \cdot 10^{-4}$ |

Table 2. Comparative study of both control strategies of GC-FLVSR responses when the DC capacitor is 3 µF.

According to these figures, it is clear that the DC-bus voltage and input currents reach their reference values with faster responses (0.01 s) and overshoots at the start of the FLVSR and with very small values of oscillations using the proposed RBSC strategy as shown in Figs. 4 and Table 2. In addition, the error indexes are much smaller than those of the PIC strategy, which demonstrates that the proposed RBSC strategy yields better performance and has the ability to enhance the integral error performance indexes compared to those based on the PIC. It should be noted that the proposed RBSC strategy is defined as the strategy that reduces those indexes.

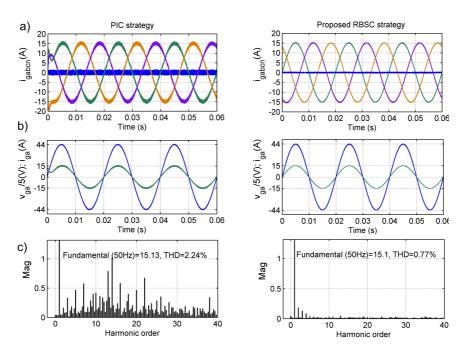

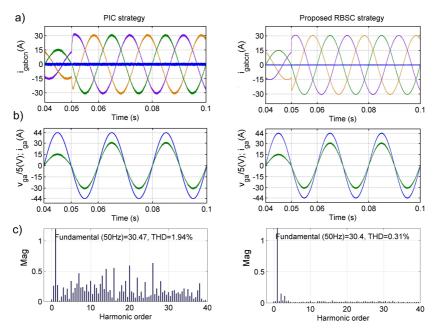

The grid currents ( $i_{gabcn}$ ), the first-phase grid voltage and its corresponding current, and the harmonic spectrum of grid currents using both control strategies are illustrated in Figs. 5. It can be observed from these figures that the grid currents are sinusoidal with lower oscillations using the proposed RBSC strategy and the maximum neutral grid current oscillation is also perfectly reduced from 1 A using the PIC strategy to 0.3 A using the proposed RBSC strategy. The grid currents are in phase with their corresponding grid voltages, which demonstrates that the maintained grid UPF is accurately achieved and the absorption of the sinusoidal currents is

A. Chebabhi, A. Kessal: DESIGN OF NEW ROBUST BACKSTEPPING CONTROL...

Fig. 4. Comparison of DC bus voltage and input currents performance when the DC capacitor is 3 µF.

also guaranteed under this transient. The total harmonic distortion (THD) is 2.24% when using the PIC strategy, but it is reduced to 0.77% when using the proposed RBSC strategy, as shown in Fig. 5c, which meets the IEEE 519 standard for current distortion limits.

Fig. 5. Grid currents, first-phase grid voltage and its corresponding current, and the harmonic spectrum of grid currents under ideal parameters. PIC strategy (on left), proposed RBSC strategy (on right).

# 4.2. Test 2 – Change of DC-bus voltage

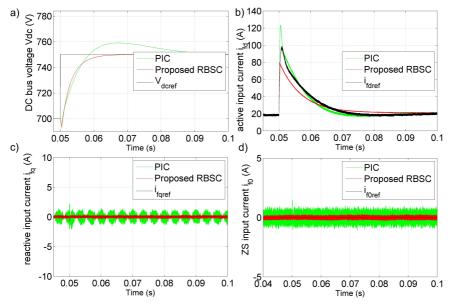

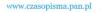

The second comparative study is performed through a test of DC bus voltage step change from 700 V to 750 V at 0.05 s, and the control performance of both control strategies is represented in Figs. 6 (a, b, c, and d). These figures compare the performance of the DC bus voltage and input currents before and after this change when the DC capacitor is 3  $\mu$ F.

Fig. 6. Comparison of DC bus voltage and input currents performance under DC-bus voltage reference change from 700 V to 750 V at 0.05s when the DC capacitor is 3  $\mu$ F.

When using the proposed RBSC, the DC-bus voltage has a very fast response (0.01 s) and tracks its reference value without an overshoot after the change and with very small oscillations after this change. The traditional PIC has an overshoot of 12 V and a settling time of 0.05 s, while the proposed RBSC has a zero overshoot and a response time of 0.01 s. The active input current reaches its reference value exactly and fast, with a fast transient time at this change and with very small oscillations after this change. The maximum overshoot of this current at the change is 125 A when using the PIC, which is significantly reduced to 80 A using the proposed RBSC.

The reactive and ZS current are kept constants at zero before and after this change and are not affected by this change, and their oscillations are very small when using the proposed RBSC strategy, which demonstrates that the grid UPF operation and the perfect decoupling of input currents as well as active and reactive powers have been accurately achieved using the proposed RBSC strategy.

# 4.3. Test 3 – Load change

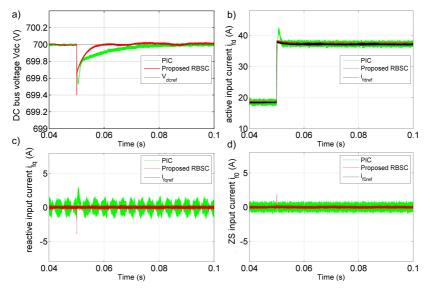

In this test scenario, a load resistance variation is achieved from 100 to 50  $\Omega$  at 0.05 s to evaluate both control strategies performance under a 100% decrease in load resistance power. The control parameters are the same as in Test 1. Figs. 7 and 8 show the control performance and dynamic responses for both control strategies for GC-FLVSR.

A. Chebabhi, A. Kessal: DESIGN OF NEW ROBUST BACKSTEPPING CONTROL...

Fig. 7. Comparison of FLVSR performance with the traditional PIC strategy and the proposed RBSC strategy under load change from 100 to 50  $\Omega$  at 0.05s with ideal parameters.

Fig. 8. Grid currents, first-phase grid voltage and its corresponding current, and the harmonic spectrum of grid currents under load change from 100 to 50  $\Omega$  at 0.05 s. PIC strategy (on left), proposed RBSC strategy (on right).

As shown in Fig. 7a, the load change causes an undershoot in the DC-bus voltage under both strategies. When the proposed RBSC is used, the DC-bus voltage remains constant near its reference value, and the undershoot is compensated after a very short transient period by

increasing the active input current as well as the active power, so that the active input current reaches its new reference value with high accuracy, stability, and very small oscillations, as shown in Fig. 7b, which demonstrates the high disturbance rejection ability of the proposed RBSC. When the proposed RBSC is compared to the PIC, the reactive and zero-sequence input currents oscillate around zero with very small oscillations, as shown in Figs. 7c and (d), confirming that the proposed RBSC ensures accurate decoupling of active and reactive input currents as well as powers.

The grid currents ( $i_{gabc}$ ), the first phase grid voltage and its corresponding current, and the grid current THD values under both control strategies are illustrated in Figs. 8a, b, and c, respectively. It can be observed from these figures that the grid currents have sinusoidal waveforms and can be kept in phase with their corresponding voltages, guaranteeing a UPF operation of the FLVSR. The THD values of the grid currents under load power change are significantly reduced from 1.94% under the traditional PIC to 0.31% using the proposed RBSC strategy, which fits the IEEE 519 standard for current distortion limits.

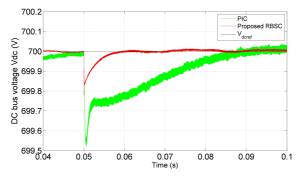

#### 4.4. Test 4 – Robustness against parameters variations

In the first scenario of this test, the DC capacity  $C_{dc}$  was increased to 6  $\mu$ F to evaluate the robustness and the disturbance rejection ability of the proposed RBSC under a 100% decrease in load resistance at 0.05 s from 100 to 50  $\Omega$ . Figs. 9 and 10 show the DC bus voltage performance and grid current THDs for both control strategies. From this comparative study, it can be observed that the PIC strategy achieves the worst performances in terms of transient time and undershoot rejection ability, while the proposed RBSC strategy has a very small undershoot and transient

Fig. 9. Comparison of FLVSR DC bus voltage performance with the traditional PIC strategy and the proposed RBSC strategy under load change from 100 to 50  $\Omega$  with  $C_{dc}$  = 6  $\mu$ F.

Fig. 10. Grid currents THDs under  $C_{dc} = 6 \ \mu\text{F}$  when the load is changed from 100 to 50  $\Omega$ . a) PIC strategy, b) the proposed RBSC strategy.

A. Chebabhi, A. Kessal: DESIGN OF NEW ROBUST BACKSTEPPING CONTROL...

time, which proves the high robustness of the proposed RBSC against DC capacity and load resistance variations and the high disturbance rejection ability.

Compared to Test 3, when the  $C_{dc}$  value is 3  $\mu$ F, the grid current THDs are increased from 0.31% to 0.35% using the proposed RBSC and from 1.94% to 2.27% using the PIC, as shown in Fig. 10, which again demonstrates the superiority of the proposed RBSC.

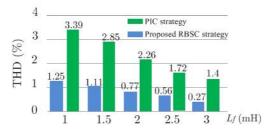

In the second scenario of this test, the filter inductance was varied from 1 to 3 mH to evaluate the robustness of both control strategies, as shown in Fig. 11. From this, it can be observed that the THDs are decreased from 1.25% to 0.27% using the proposed RBSC and from 3.39% to 1.4% using the PIC, which also proves the high robustness of the proposed RBSC against filter inductance variations.

Fig. 11. Comparison of grid currents THDs versus filter inductor variation with the PIC and the proposed RBSC.

# 5. Conclusions

This paper has proposed a RBSC for a GC-FLVSR with consideration of uncertainties for the task of controlling the DC bus voltage and input currents simultaneously, which leads to high robustness against parametric uncertainties. Moreover, it employs four controllers: including three for the input currents and one for the DC bus voltage. Based on the principle of Lyapunov functions and with consideration of uncertainties, the proposed RBSC strategy can obtain the FLVSR input reference voltages.

The theoretical study and the effectiveness of the proposed control strategy are confirmed using PIL co-simulations using the STM32F407 microcontroller discovery-development-board. Compared to the traditional PIC, the proposed RBSC strategy can obtain lower input current THDs and reduce DC bus voltage ripples with high dynamic response. Thus, it can be observed that the proposed RBSC presents numerous advantages with regard to the linear control strategy, where: the most significant are: sinusoidal currents with high quality; stable DC bus voltage with lower ripples; fast response time; unity power factor; high robustness against parametric variations; easy implementation; ability to enhance the integral DC-bus voltage and input current errors performance indexes. It also offers rather high voltage disturbance rejection ability. Therefore, it is concluded that the proposed RBSC strategy is a more favourable and feasible scheme for grid-connected four leg PWM converters.

## References

Lu, J., Golestan, S., Savaghebi, M., Vasquez, J. C., Guerrero, J. M., & Marzabal, A. (2017). An enhanced state observer for DC-link voltage control of three-phase AC/DC converters. *IEEE Transactions on Power Electronics*, 33(2), 936–942. https://doi.org/10.1109/TPEL.2017.2726110

- [2] Song, T., Wang, P., Zhang, Y., Gao, F., Tang, Y., & Pholboon, S. (2020). Suppression Method of Current Harmonic for Three-Phase PWM Rectifier in EV Charging System. *IEEE Transactions on Vehicular Technology*, 69(9), 9634–9642. https://doi.org/10.1109/TVT.2020.3005173

- [3] Rabie, D., Senjyu, T., Alkhalaf, S., Mohamed, Y. S., & Shehata, E. G. (2021). Study and analysis of voltage source converter control stability for HVDC system using different control techniques. *Ain Shams Engineering Journal*, 12(3), 2763–2779. https://doi.org/10.1016/j.asej.2020.12.013

- [4] Zhang, R., Lee, F. C., & Boroyevich, D. (2000, June). Four-legged three-phase PFC rectifier with fault tolerant capability. *Proceedings of the IEEE 31st Annual Power Electronics Specialists Conference*, Galway, Ireland, 1, 359–364. https://doi.org/10.1109/PESC.2000.878878

- [5] Kaszewski, A., Gałecki, A., Ufnalski, B., & Grzesiak, L. M. (2014). State-space current control for four-leg grid-connected PWM rectifiers with active power filtering function. *Proceedings of the IEEE* 16th International Power Electronics and Motion Control Conference and Exposition, Antalya, Turkey, 1265–1271. https://doi.org/10.1109/EPEPEMC.2014.6980686

- [6] Miveh, M. R., Rahmat, M. F., Ghadimi, A. A., & Mustafa, M. W. (2016). Control techniques for three-phase four-leg voltage source inverters in autonomous microgrids: A review. *Renewable and Sustainable Energy Reviews*, 54, 1592–1610. https://doi.org/10.1016/j.rser.2015.10.079

- [7] Mandrioli, R., Viatkin, A., Hammami, M., Ricco, M., & Grandi, G. (2020). A comprehensive AC current ripple analysis and performance enhancement via discontinuous PWM in three-phase four-leg grid-connected inverters. *Energies*, 13(17), 4352. https://doi.org/10.3390/en13174352

- [8] Olives-Camps, J. C., Mauricio, J. M., Barragán-Villarejo, M., & Matas-Díaz, F. J. (2019). Voltage control of four-leg VSC for power system applications with nonlinear and unbalanced loads. *IEEE Transactions on Energy Conversion*, 35(2), 640–650. https://doi.org/10.1109/TEC.2019.2957185

- [9] Chebabhi, A., Fellah, M. K., Kessal, A., & Benkhoris, M. F. (2015). Comparative study of reference currents and DC bus voltage control for Three-Phase Four-Wire Four-Leg SAPF to compensate harmonics and reactive power with 3D SVM. *ISA Transactions*, 57, 360–372. <u>https://doi.org/10.1016/j.isatra. 2015.01.011</u>

- [10] Kumar, A. P., Kumar, G. S., & Sreenivasarao, D. (2020). Model predictive control with constant switching frequency for four-leg DSTATCOM using three-dimensional space vector modulation. *IET Generation, Transmission & Distribution*, 14(17), 3571–3581. https://doi.org/10.1049/iet-gtd.2019.1775

- [11] Yin, H., & Dieckerhoff, S. (2015). Experimental comparison of DPC and VOC control of a three-level NPC grid connected converter. *Proceedings of the IEEE 6th International Symposium on Power Electronics for Distributed Generation Systems*, Aachen, Germany, 1–7. <u>https://doi.org/10.1109/PEDG</u>. 2015.7223072

- [12] Dheepanchakkravarthy, A., Akhil, S., Venkatraman, K., Selvan, M. P., & Moorthi, S. (2018). Performance analysis of FPGA controlled four-leg DSTATCOM for multifarious load compensation in electric distribution system. *Engineering Science and Technology, an International Journal*, 21(4), 692–703. https://doi.org/10.1016/j.jestch.2018.05.004

- [13] Djerioui, A., Houari, A., Saim, A., Aït-Ahmed, M., Pierfederici, S., Benkhoris, M. F., & Ghanes, M. (2019). Flatness-based grey wolf control for load voltage unbalance mitigation in four-leg voltage source inverters. *IEEE Transactions on Industry Applications*, 56(2), 1869–1881. <u>https://doi.org/10.1109/</u>TIA.2019.2957966

A. Chebabhi, A. Kessal: DESIGN OF NEW ROBUST BACKSTEPPING CONTROL ...

- [14] Pichan, M., & Rastegar, H. (2017). Sliding-mode control of four-leg inverter with fixed switching frequency for uninterruptible power supply applications. *IEEE Transactions on Industrial Electronics*, 64(8), 6805–6814. https://doi.org/10.1109/TIE.2017.2686346

- [15] Pichan, M., Arab Markadeh, G., & Blaabjerg, F. (2020). Continuous finite-time control of four-leg inverter through fast terminal sliding mode control. *International Transactions on Electrical Energy Systems*, 30(6), e12355. https://doi.org/10.1002/2050-7038.12355

- [16] Chebabhi, A., Fellah, M. K., Kessal, A., & Benkhoris, M. F. (2016). A new balancing three level three dimensional space vector modulation strategy for three level neutral point clamped four leg inverter based shunt active power filter controlling by nonlinear back stepping controllers. *ISA Transactions*, 63, 328–342.

- [17] Wang, X., Sun, D., & Zhu, Z. Q. (2017). Resonant-based backstepping direct power control strategy for DFIG under both balanced and unbalanced grid conditions. *IEEE Transactions on Industry Applications*, 53(5), 4821–4830. https://doi.org/10.1109/TIA.2017.2700280

- [18] Li, J., Liu, Z., & Su, Q. (2019). Improved adaptive backstepping sliding mode for a three-phase PWM converter. *IET Control Theory & Applications*, 13(6), 854–860. <u>https://doi.org/10.1049/iet-cta.</u> 2018.5453

- [19] Wai, R. J., & Yang, Y. (2019). Design of backstepping direct power control for three-phase PWM rectifier. *IEEE Transactions on Industry Applications*, 55(3), 3160–3173. <u>https://doi.org/10.1109/TIA.2019.2893832</u>

- [20] Alyoussef, F., & Kaya, I. (2019). A review on nonlinear control approaches: sliding mode control backstepping control and feedback linearization control. *International Engineering and Natural Sciences Conference*, (Vol. 2019, pp. 608–619).

- [21] Zamzoum, O., Derouich, A., Motahhir, S., El Mourabit, Y., & El Ghzizal, A. (2020). Performance analysis of a robust adaptive fuzzy logic controller for wind turbine power limitation. *Journal of Cleaner Production*, 265, 121659. https://doi.org/10.1016/j.jclepro.2020.121659

- [22] Cheddadi, Y., Errahimi, F., & Es-sbai, N. (2018). Design and verification of photovoltaic MPPT as an automotive-based embedded software. *Solar Energy*, 171, 414–425. <u>https://doi.org/10.1016/j.solener.</u> 2018.06.085

Ali Chebabhi was born in M'sila, Algeria, in 1985. In 2009, he received the degree of engineer in electrical engineering from the University of M'sila, Algeria. In 2011, he was granted the M.Sc. degree in power electronics from the University of Sidi-bel-Abbès, Algeria. He also received his Ph.D. in power electronics from the University of Sidi-bel-Abbès, Algeria, in 2016 and the post-doctoral degree in May 2018. He is currently assistant professor in the university of M'sila, Al-

geria. His fields of interest are control of electrical power systems and especially grid connected converters, multi-converter system embarked network and renewable energy.

Abdelhalim Kessal was born in Bordj Bou Arreridj, Algeria in 1975. He is currently full professor at the Department of Electrical Engineering and head of the Electro-Energetic Converters Research Team at the Laboratory of Materials Physics, Radiation and Nanostructures, Bordj Bou Arreridj University, Algeria. In 1997, He received the degree of engineer in electrical engineering from university of Setif, Algeria. Next, he received the degree of M.Sc. in electrical engineering and

Ph.D. in power electronics from the same university, in 2012. He was once head of the Department Electromechanics and the dean of Sciences and Technology Faculty at Bordj Bou Arreridj University. Presently, he holds the position of Vice Rector. His areas of interest are power electronic systems, renewable energy resources, trans active control and intelligent technologies.