ARCHIVES OF ELECTRICAL ENGINEERING

VOL. 72(2), pp. 373-389 (2023)

DOI 10.24425/aee.2023.145414

# Boosting resonant switched-capacitor voltage tripler

MACIEJ CHOJOWSKI™, ROBERT SOSNOWSKI, MARCIN BASZYŃSKI

AGH University of Science and Technology

Poland

e-mail: <sup>™</sup>chojo@agh.edu.pl

(Received: 26.05.2022, revised: 21.11.2022)

**Abstract:** This elaboration presents the concept of a unidirectional DC–DC switched-capacitor converter operating as a voltage tripler. The system consists of two resonant cells with switched capacitors and chokes. This proposed converter topology achieves low voltages on semiconductor switches (diodes and transistors) compared to the classic SC series-parallel converter or the boost topology. The output voltage on the capacitors is reduced in the proposed converter because it is divided into two series-connected capacitors with asymmetric distribution. The presented results describe the analytical description of the system operation and the analytical equation for semiconductor currents. A simulation and experimental results have been performed. The system efficiency and three voltage gain values were measured in the experimental setup. The efficiency measured was also compared with the analytical determination curve for loss analysis and further converter optimization.

Key words: boost topology, DC-DC converters, switched-capacitor converter

# 1. Introduction

Switched-capacitor (SC) systems are often used as DC–DC boost topology [1, 2]. The SC converters are designed to reduce the number or inductance value of power choke. As a result, it allows one to achieve a smaller size and lower weight of the converter system.

Works [3, 4] present the systems that allow obtaining the output voltage twice the value of the input voltage (the voltage doubler), due to the use of series resonance effect, which allows the reduction of losses of switching transistors. Zero current switching (ZCS) leads to noticeably high efficiency (97.0–98.5%). Moreover, these circuits consist of a relatively small number of elements, i.e. two transistors, two diodes, a resonant capacitor, resonant choke and an output capacitor.

© 2023. The Author(s). This is an open-access article distributed under the terms of the Creative Commons Attribution-NonCommercial-NoDerivatives License (CC BY-NC-ND 4.0, https://creativecommons.org/licenses/by-nc-nd/4.0/), which permits use, distribution, and reproduction in any medium, provided that the Article is properly cited, the use is non-commercial, and no modifications or adaptations are made. 374

Recently, many topologies of the Dickson family have been discussed in [5–8]. Interleaved circuits with switched capacitors can achieve high gain values [5, 7, 8] or work as a voltage lowering circuit [6].

An example of the SC converter allowing one to obtain various voltage gain is presented in [9]. The value of the output voltage depends on the duty cycle of the control pulses. Voltage stresses of the switches are lower than the output voltage [9].

The circuit described in [10] has three voltage outputs with maximum gains equal to two, four and six, respectively. The voltage gain can be smoothly regulated by changing the activation time of one of the transistors [10]. The converter uses four transistors and the maximum voltage of the switches is limited to the input voltage value or twice its value.

The circuits described in [11] and [12] have a voltage gain equal to three. It uses two transistors, the switching losses are limited by the phenomenon of series resonance, which results in soft switching. An important feature of these converters is the common grounding of the input and output voltages.

Boost DC–DC converters are used, among others, in hybrid cars to ensure the appropriate level of input voltage for the motor inverter [13]. In addition, they are used in cars to power lamps [14] and in systems powered by fuel cells or photovoltaic installations [9].

The DC–DC converters with the topology presented in [15–17] are similar to those presented in [3–12], which can also be used as power factor improvement (PFC) circuits. Paper [15] describes a three-level boost converter. The converter [15] operates in the discontinuous conduction mode as a PFC converter with spread spectrum frequency modulation. The proposed control method allows one to reduce electromagnetic interference and increase overall efficiency.

Article [16] describes the three-level DC–DC buck converter of the switched-inductor voltage-lift type. This circuit includes three transistors. Two of them are switched complementary. When the duty cycle of the control signal in the third transistor changes, the circuit voltage gain is adjusted. It is possible to obtain enormous gain values greater than 10, while maintaining low voltage stresses of the transistors. The circuit from [15,16] also has a modification (replacing the diodes with transistors), which allows two-way energy transfer as in the classic two-level boost circuit [17]. The SC family of converters can control the output voltage [3, 10], similar to the previous converter [15,16].

The control can be carried out by changing the duty cycle, switching frequency or phase shift of the PWM signals (in the case of systems with more switches).

The proposed converter has a topology close to the automatic interleaved Dickson switched capacitor converter (AIDSCC) described in [5]. An important difference is the way the  $C_{\rm out2}$  capacitor is connected. In the proposed system, it is connected between the negative pole of the output voltage and the negative pole of the input voltage (the grounding of the system). In the AIDSCC, it is connected between the negative pole of the output voltage and the positive pole of the input voltage. This topology change has significant implications.

The AIDSCC voltage  $U_{\rm out2}$  is  $-2U_{\rm in}$ . Therefore, it is necessary to select a capacitor for a voltage value twice as high as that of the considered system. Furthermore, for the AIDSCC circuit, the output voltages  $U_{\rm out1}$  and  $U_{\rm out2}$  do not have common grounding, as is the case in the proposed circuit. The proposed converter can be used in systems where the input and output common grounding is not required. For this reason, it could be suitable in renewable systems as the front-end DC-DC power conversion, auxiliary power supplies, battery equalizer, and

in automotive applications, as well as in high-intensity discharge lamp supply units in vehicle headlights [10, 17, 18].

The paper is organized as follows. Section II presents the theoretical aspects of the proposed DC–DC converter with an analytical description. Section III contains the results of the simulation described in Section II. Section IV provides laboratory measurements of the proposed system. The waveforms of the voltages and the current of the selected power elements are presented. An efficiency test with voltage gain for a variable load is included in the chart.

# 2. Concept of the novel converter

### 2.1. Principle of operation

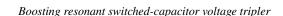

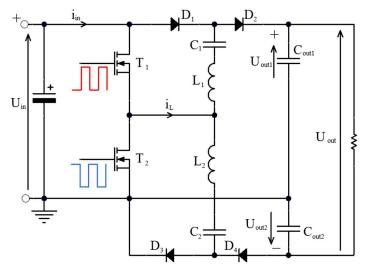

The proposed converter is shown in Fig. 1. The principle of its operation assumes that the transistors are switched on alternately with a constant 50% duty cycle in the dead time. For analytical considerations, the dead time has been omitted. The complementary switching of the transistors causes the current to flow through the chokes ( $L_1$  and  $L_2$ ) and the charging capacitors  $C_1$  and  $C_2$  from the input source (Fig. 2). The topology in Fig. 1 can also be extended by many cells, e.g. as in [3,5,7,10–12]. This extension allows one to increase the voltage gain by adding more diodes and capacitors [11] (or capacitors with extra chokes [3,10]). The modification of the converter assumes that the two chokes are replaced by one L choke.

Fig. 1. The novel concept of unidirectional DC–DC high-voltage-gain converter (voltage gain G = 3, G = 2 or G = -1 and the number of switches s = 2)

Overcharged capacitors will provide energy for the output capacitors  $C_{\text{out1}}$  and  $C_{\text{out2}}$ . The circuit with the  $D_1$  and  $D_2$  diodes together with the  $C_{\text{out1}}$  capacitor forms a double voltage  $(2 - U_{\text{in}})$ , while the  $D_3$  and  $D_4$  diodes with the  $C_{\text{out2}}$  capacitor are the circuit that ensures the

input voltage inversion  $(-U_{in})$ . Consequently, the output voltage can be described as:

$$U_{\text{out}} = U_{\text{out}1} - U_{\text{out}2} = 2 \cdot U_{\text{in}} - (-U_{\text{in}}) = 3 \cdot U_{\text{in}}.$$

(1)

Fig. 2. The operation state: charging (a); discharging (b)

## 2.2. Input current determination

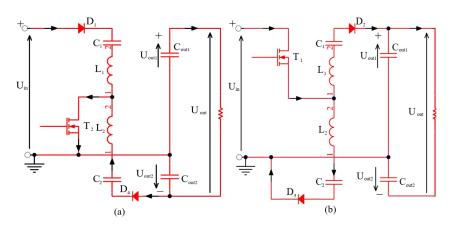

Figure 3 shows the theoretical waveforms for the proposed control. It should be emphasized that the value of the input current  $i_{\rm in}$  indicates the current after the filter capacitor. Operation with a frequency close to the resonant  $f_0$  ( $L_1$  and  $L_2$  with  $C_1$  and  $C_2$  capacitors, respectively) results in a sinusoidal current with the value  $I_{\rm in\ max}$ . In the second half-period, when the transistor

Fig. 3. Theoretical waveforms of the logic signals for transistors  $T_1$  and  $T_2$  with idealized input current

$T_1$  is turned on, the input voltage and the volt-age on the capacitors are applied to the output capacitors. As a consequence, a current flows through the source with a maximum value twice as low ( $I_{\text{in max}}/2$ ). The average value of the input current can be defined as:

Boosting resonant switched-capacitor voltage tripler

$$I_{\text{in avg}} = \frac{1}{T} \int_{0}^{T} i_{\text{in}}(t) dt = \frac{1}{T} \int_{0}^{T/2} I_{\text{in max}} \sin \omega t dt + \frac{1}{T} \int_{T/2}^{T} \frac{I_{\text{in max}}}{2} \sin(\omega t - \pi) dt.$$

(2)

The average value of the input current is:

$$I_{\text{in avg}} = \frac{I_{\text{in max}}}{\pi} + \frac{I_{\text{in max}}}{2\pi} = \frac{3}{2\pi}I_{\text{in max}}.$$

(3)

The maximum value of the input current is:

$$I_{\text{in max}} = \frac{2\pi}{3} I_{\text{in avg}} = 2\pi I_{\text{out}}. \tag{4}$$

## 2.3. Determination of the current stresses of components

Assuming the ideal half-wave sinusoidal current for diodes and transistors, the RMS current of the switches can be described as:

$$I_{T \text{ rms}} = I_{T_1 \text{ rms}} = I_{T_2 \text{ rms}}.$$

(5)

In addition, it can be calculated by:

$$I_{T \text{ rms}} = \sqrt{\frac{1}{T} \int_{0}^{T} i_{T}^{2}(t) dt} = \sqrt{\frac{1}{T} \int_{0}^{T/2} (2\pi I_{\text{out}} \sin \omega t)^{2} dt} = 2\pi I_{\text{out}} \sqrt{\frac{1}{4}} = \pi I_{\text{out}} = \frac{I_{\text{in max}}}{2}.$$

(6)

There, the average diode currents for all diodes are equal:

$$I_{Davg} = I_{D_1avg} = I_{D_2avg} = I_{D_3avg} = I_{D_4avg},$$

(7)

where the mean value is:

$$I_{Davg} = \frac{1}{T} \int_{0}^{T} i_{D}(t) dt = \frac{1}{T} \int_{0}^{T/2} \pi I_{out} \sin \omega t dt = -\frac{1}{2} I_{out} (\cos \pi - \cos 0) = I_{out} = \frac{I_{in \, max}}{2\pi}.$$

(8)

The sinusoidal shape of the inductor (and resonant capacitor) current means that the value of the inductor RMS leads to:

$$I_{L \, \text{rms}} = I_{C \, \text{rms}} = \pi \frac{\sqrt{2}}{2} I_{\text{out}} = \frac{\sqrt{2} I_{\text{in max}}}{4} \,.$$

(9)

The output capacitor current equals:

$$I_{Cout\,rms} = \pi I_{out} - I_{out} \,. \tag{10}$$

#### 2.4. Voltage stresses of components

The maximum voltage values of the diodes and transistors are approximately equal to the input voltage.

$$U_{D \max} = U_{T \max} = U_{\text{in}}. \tag{11}$$

The mean voltages on resonant capacitors have an approximately constant average value and amount to:

$$U_{C_1 \text{avg}} = U_{C_2 \text{avg}} = U_{\text{in}} \,.$$

(12)

The voltages for the output capacitors are approximately equal to:

$$U_{Cout1} = 2U_{in}, (13)$$

$$U_{\text{Cout2}} = -U_{\text{in}} \,, \tag{14}$$

$$U_{Cout} = 3U_{in}. (15)$$

# 2.5. Efficiency analysis

The converter efficiency equals:

$$\eta \triangleq \frac{P_{\text{out}}}{P_{\text{in}}} = \frac{P_{\text{in}} - \Delta P_C - \Delta P_{\text{SW}} - \Delta P_{Qrr}}{P_{\text{in}}} = 1 - \frac{\Delta P_C + \Delta P_{\text{SW}} + \Delta P_{Qrr}}{P_{\text{in}}}, \quad (16)$$

where:  $\Delta P_C$  represents the conduction losses,  $\Delta P_{\rm SW}$  represents the switching losses. The turn-off switching losses are practically equal to zero, due to the soft switching (ZCS). However, there is a turn-on switching loss associated with charging and discharging the output capacitances of the FETs [20]. The total switching power losses  $\Delta P_{\rm SW}$  are equal only to the losses  $E_{\rm on}$ :

$$\Delta P_{\rm on} = \sum_{l=1}^{2} E_{\rm on} l f_{\rm S} . \tag{17}$$

The total conduction losses are the sum of the conduction loss  $\Delta P_T$  in the transistors, the loss  $\Delta P_D$  in the diodes, and the loss  $\Delta P_L$  in inductance:

$$\Delta P_{C} = \Delta P_{T} + \Delta P_{D} + \Delta P_{L} + \Delta P_{C} = \sum_{k=1}^{2} R_{DS(\text{on})k} I_{Tk}^{2} + \sum_{l=1}^{4} V_{Fl} I_{Dlavg}$$

$$+ \sum_{z=1}^{2} R_{L-\text{ESR}} I_{Lz}^{2} + \sum_{z=1}^{2} R_{C-\text{ESR}} I_{Lz}^{2} + \sum_{z=1}^{2} R_{C\text{out-ESR}} (I_{C\text{out rms}})^{2}, \qquad (18)$$

where:  $R_{DS(\text{on})}$  is the MOSFET turn-on resistance,  $V_{Fl}$  is the diode voltage drop,  $R_{AC}$  is the inductor equivalent resistance (measured by an impedance analyzer for an operating frequency of 100 kHz),  $R_{C\text{-ESR}}$  is the resonant capacitor equivalent resistance,  $R_{\text{Cout-ESR}}$  is the output capacitor equivalent resistance. The turn-off power loss generated by the switching diode  $\Delta P_{Orr}$  is:

$$\Delta P_{Qrr} = \sum_{l=1}^{4} f_S V Q_{rrl} \,, \tag{19}$$

where V is the diode blocking voltage and  $Q_{rr}$  is the diode reverse recovery charge. The overall efficiency equals:

Boosting resonant switched-capacitor voltage tripler

$$\eta_{TOSCVM} = 1 - \frac{\left[\pi^{2} \left(R_{L-ESR} + R_{C-ESR}\right) I_{\text{out}} + 2R_{C\text{out-ESR}} \left(\pi I_{\text{out}} - I_{\text{out}}\right)^{2}\right]}{P_{\text{in}}} - \frac{2\pi^{2} R_{DS(\text{on})k} I_{\text{out}}^{2} + 4V_{Fl} I_{\text{out}}}{P_{\text{in}}} - \frac{2f_{S}(2U_{\text{in}}Q_{rr} + E_{\text{on}})}{P_{\text{in}}}.$$

(20)

# 3. Simulation results

#### 3.1. Steady state operation

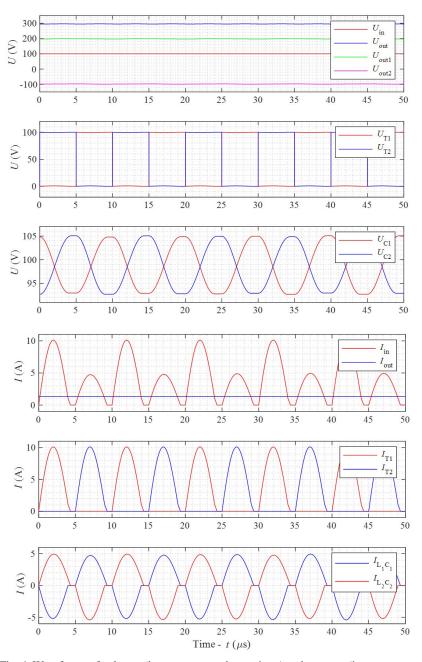

The results in Fig. 4 show only the steady state operation simulation of the power converter (simulation parameters are listed in Table 1). Key values for voltage or current have been defined for chokes, capacitors, and semiconductor elements. The simulation results confirmed (Fig. 4) that both transistors have a similar RMS current value, and the voltage across the transistors is equal to the input voltage. The simulation results obtained are approximately consistent with the theoretical runs. The current waveforms differ to some extent from the expected ones because of the inconsistency of the elements (e.g. the conduction resistance of transistors and voltage drops on the diodes).

Parameter name **Symbol** Value Unit Inductance  $L_1, L_2$ 1.7 μΗ Capacitance  $C_1, C_2$ 1.1 μF 80 Resistance drain-source  $m\Omega$  $R_{DS(on)}$ Diodes 1-4 forward voltage  $V_F$ 0.5 V V Input voltage  $U_{\rm in}$ 100 Switching frequency 100 kHz  $f_{s}$

Table 1. Parameters of the converter and input voltage for the simulation model

The system analysis shows that semiconductor elements have identical current loads and voltage stresses, which is a great advantage of the system. Resonance capacitors also have the same voltage with the same effective value.

For the same parameters (Table 1) of the simulation system, the gain values were tested at different outputs of the system (Table 2).

The values of the load resistances from Table 2 have been selected, so that the output current is approximately 1 A. The load of one of the outputs has a relatively small influence on the values of the gains. In the case of no load, the voltages of the output capacitors increase significantly. The values of these voltages are limited by losses in the system.

Fig. 4. Waveforms of voltages (input, output and capacitors) and currents (input, output, transistors and LC branches) of proposed converter operating. Matlab/Simulink results for 400 W of output power ( $U_{\rm in}=100~{\rm V}$  and  $f=100~{\rm kHz}$ )

$R_1=200~\Omega$  $R_1 = \infty$  $R_1 = \infty$  $R_1=200~\Omega$  $R_1 = \infty$ **Parameters**  $R_2 = \infty$  $R_2=100~\Omega$  $R_2 = \infty$  $R_2=100~\Omega$  $R_2 = \infty$  $R = \infty$  $R = \infty$  $R = 300 \ \Omega$  $R = 300 \Omega$  $R = \infty$ 1.99 1.95 2.53 2.07 1.97  $G_1$ -1.07-0.99-0.97-0.95 $G_2$ -1.50 $G = G_1 - G_2$ 3.06 3.06 2.94 2.91 4.03

Table 2. Simulation results (input voltage 100 V and frequency 100 kHz)

# 4. Experimental results

# 4.1. Experimental setup

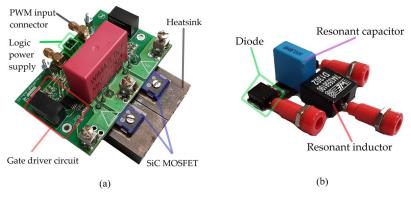

The proposed DC-DC converter was experimentally investigated to verify the operation principle, switching concepts, voltage gain, voltage stresses on switches, power losses, efficiency, and temperature field distribution. Table 3 sums up the major converter (Fig. 5) parameters and

Table 3. Parameters of the laboratory setup

| Parameter                                                | Value                                                                                                                                |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Input voltage $U_{\rm in}$                               | 100 V                                                                                                                                |

| Input capacitor                                          | EPCOS electrolytic 50 $\mu$ F $\pm 20\%$ with MKP 4.7 $\mu$ F $\pm 5\%$ and MKP 1 $\mu$ F $\pm 5\%$                                  |

| Output capacitor $C_{\text{out}1}$ and $C_{\text{out}2}$ | 4.7 μF ±5% (MKP capacitor) $R_{Cout-ESR} = 5.8 \text{ m}\Omega$                                                                      |

| SC capacitance $C_1$ and $C_2$                           | 1100 nF, $R_{C\text{-ESR}} = 2.6 \text{ m}\Omega$                                                                                    |

| Inductor – $L_1$ and $L_2$                               | 1.7 μΗ                                                                                                                               |

| Inductors $R_{DC}$ (DCR) and $R_{AC}$                    | $R_{DC} = 1.4 \text{ m}\Omega R_{AC} = 115.1 \text{ m}\Omega \text{ for } 100 \text{ kHz}$                                           |

| Resonant frequency                                       | $f_0 \approx 116.4 \text{ kHz}$                                                                                                      |

| Operating frequency                                      | $f_S \approx 00 \text{ kHz}$                                                                                                         |

| SiC MOSFET transistors                                   | C3M0060065D ( $V_{DS}$ = 650 V, $I_{D}$ = 29 A,<br>$R_{DS(\text{on})}$ = 60 m $\Omega$ )                                             |

| Single-channel driver for high side and low side         | 1EDI60H12AH – 6.0 A high-side isolated gate driver                                                                                   |

| Isolated DC–DC supply for driver                         | MGJ2D051505SC ( $P = 2$ W, $U_{input} = 5$ V,<br>$U_{input} = +15$ V/–5 V)                                                           |

| Diodes                                                   | VB60170G-E3 ( $I_F = 2 \times 30 \text{ A}, V_{RRM} = 170 \text{ V},$<br>$V_F = 0.65 \text{ V} \text{ at 5 A}, 25^{\circ}\text{C}$ ) |

| PWM generator                                            | External board DE10-lite Control Board                                                                                               |

| Dead time                                                | 50 ns                                                                                                                                |

laboratory setup for the experiment. The prototyping half bridge (Fig. 5(a)) was used to check only the topology operation. The volume and efficiency optimization were not the main goals of the article.

Fig. 5. Experimental board: half bridge (a); with resonant LC circuit diodes (b)

#### 4.2. Operation of the converter

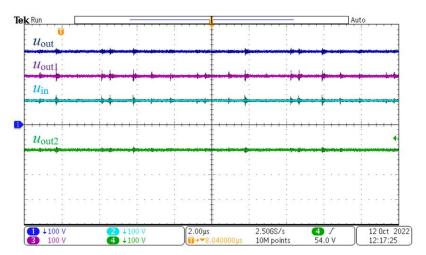

The subsection presents the results for the steady state. The Tektronix TCP0030A current probe with a 120 MHz band [21] was attached to the MDO3000 series oscilloscope [22], and passive TPP1000 probes (CAT II up to 300 V) with a 1 GHz band were used to measure the voltage in the components [23]. The results of the measurement of the input voltage and possible output voltages are shown in Fig. 6.

Fig. 6. Experimental waveforms of the converter for  $P_{\rm in} \approx 400$  W and  $U_{\rm in} = 100$  V – output voltage  $u_{\rm out}$  (CH1), input voltage  $u_{\rm in}$  (CH2), first output voltage with  $G = 2u_{\rm out1}$  (CH3) and second output voltage with  $G = -1u_{\rm out2}$  (CH4s)

Boosting resonant switched-capacitor voltage tripler

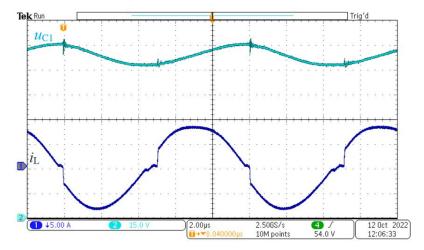

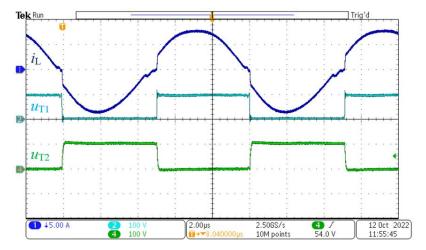

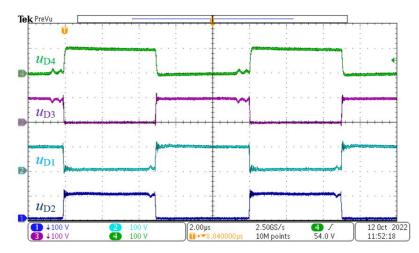

The results of the choke current measurement  $i_L$  ( $i_{L1} + i_{L2}$ ) and the voltages of the resonant capacitor  $C_1$  are shown in Fig. 7. The results are similar to the simulation results in Fig. 4. The voltage waveforms for transistors (with resonant inductor current) and diodes are shown in Fig. 8 and Fig. 9, respectively. In a steady state, the voltage value is close to the input voltage ( $U_{\rm in} \approx 100$  V). The visible overshoot is the result of parasitic inductance in the power circuit.

Fig. 7. Experimental waveforms of the converter for  $P_{\rm in}\approx 400~{\rm W}$  and  $U_{\rm in}=100~{\rm V}$  – resonant inductor  $(i_L=i_{L1}+i_{L2})$  current (CH1) and voltages across resonant capacitor  $C_1$  (CH2)

Fig. 8. Experimental waveforms of the converter for  $P_{\rm in}\approx 400~{\rm W}$  and  $U_{\rm in}=100~{\rm V}$  – resonant inductor  $(i_L=i_{L1}+i_{L2})$  current (CH1) and voltages across transistors  $T_1$  (CH2) and  $T_2$  (CH4)

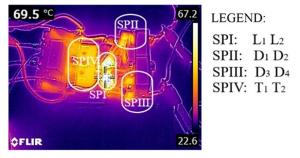

Figure 10 shows the result of the thermography of the converter operating at a power of  $P_{\text{out}} \approx 375 \text{ W}$ . These results show that the heat dissipation in switches and diodes is not significant.

384

Fig. 9. Experimental waveforms of the converter for  $P_{\rm in} \approx 400~{\rm W}$  and  $U_{\rm in} = 100~{\rm V}$  – voltages across diodes  $D_2$  (CH1),  $D_1$  (CH2),  $D_3$  (CH3) and  $D_4$  (CH4)

However, you can observe a concentration of heat near the resonance coil. The  $L_1$  choke (+69.5°C) is the hottest point in the power circuit. The high temperature is caused by the lack of an active cooling system.

Fig. 10. An infrared photo of the converter during constant operation for 600~W – transistors with heat-sink and no forced air flow

# 4.3. Efficiency and voltage gain

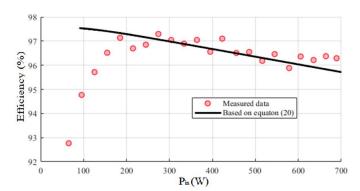

Figure 11 shows the graph of efficiency vs the output power function. A series of measurements were performed at a constant switching frequency of  $f_S = 110$  kHz. Efficiency was measured using a Yokogawa WT 1500 power analyzer [24]. The maximum efficiency of the converter was equal to  $\eta_{\text{max}} = 97.29\%$ .

The curve plotted on the basis of the results from Eq. (20) for the parameters in Table 3 was added to the results. The equivalent resistance value for a choke was determined by the impedance analyzer  $R_{AC} = 115.1 \text{ m}\Omega$  [25]. Other parameters are specified in the technical doc-

Boosting resonant switched-capacitor voltage tripler

Fig. 11. Efficiency vs output power ( $U_{in} = 100 \text{ V}$  and  $f_S \approx 100 \text{ kHz}$ )

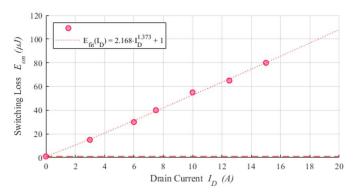

umentation [26, 27]: the transistor resistance  $R_{DS(\text{on})\text{ max}} = 80 \text{ m}\Omega$ ,  $C_{oss}$  stored energy  $E_{oss}1 \text{ µJ}$  for 100 V (marked with dashed line in Fig. 11) and the turn-on energy were calculated based on the current value (Fig. 12) and diode forward voltage  $V_F = 0.65 \text{ V}$ .

Fig. 12. Turn-on losses vs drain current for 100 V and  $V_{GS} = -4 \text{ V/+5 V}$

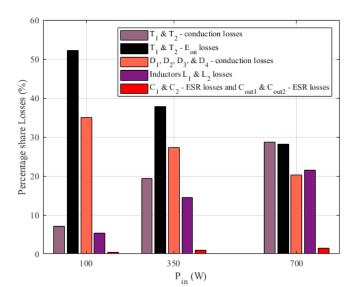

The analytical curve describing the losses in the proposed converter allows one to determine the percentage of loss for each of the components (Fig. 13). The losses are mainly caused by the conduction resistances of the MOSFETs (37% for 350 W) and the diode forward losses (27% for 350 W). Transistor conduction losses and inductor losses ( $R_{AC}$  equivalent resistance) are significant for high load (700 W). The summarized capacitors conduction losses have a slight effect on overall efficiency (< 2%). Based on Fig. 13, the direction of optimization of the system can be determined. The diode turn-off power losses  $\Delta P_{Qrr}$  were assumed neglected because there was not information on the  $Q_{rr}$  recovery charge in datasheet [25].

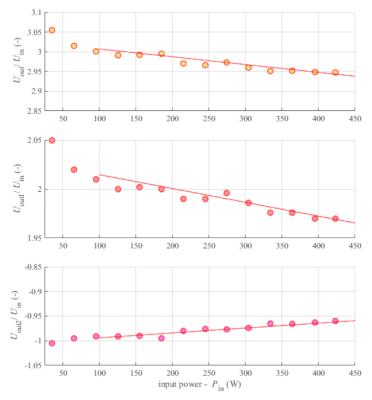

Figure 14 shows the measured voltage gains as a function of the output power (in the range from 50 to 375 W) – the voltage variation (for all possible outputs) can be determined by a linear relationship.

M. Chojowski, R. Sosnowski, M. Baszyński

Fig. 13. Losses analysis of the converter for 100 W, 350 W and maximum input power 700 W

Fig. 14. Voltage gain vs output load ( $U_{\rm in}$  = 100 V and  $f_S \approx$  100 kHz)

#### 4.4. Output voltage control

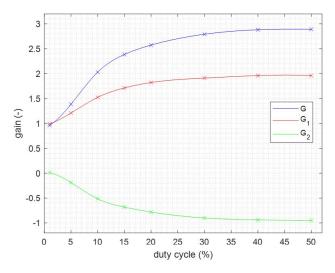

There is a possibility to control output voltages by changing the duty cycle of transistors control signals. However, only for the value of a duty cycle near to 50%, operating with zero current switching is possible. Different duty cycle values will result in the transistor turning-off while charging or discharging switched capacitors. This will result in hard turn-off and increase switching losses (no ZCS during turn-off transient process).

There are two ways of changing the duty cycle. The first is reducing the duty cycle value for both transistors, maintaining a shift in time equal to half of the switching period. The second way is reducing (or alternatively increasing) the duty cycle for transistor  $T_1$ , and controlling transistor  $T_2$  is the negation of the former. In both options, the gain vs duty cycle characteristic is similar.

Figure 15 shows the relation between the voltage gains and duty cycle for the first way of changing the duty cycle. For a duty cycle near to zero,  $G_1$  is close to 1,  $G_2$  is close to zero and as a consequence G is approximately equal to 1. The absolute values of gains are growing nonlinearly with an increase in duty cycles.

Fig. 15. Gain vs  $T_1$  duty cycle ( $T_2$  control is a negation of  $T_1$  control) for 300 W for resistive load 220  $\Omega$  ( $U_{\rm in} = 100 \text{ V}$  and  $f_S = 100 \text{ kHz}$ )

# 5. Conclusions

This paper presents a general-concept topology and switching methods of the proposed DC–DC converter. The research results presented in this paper confirm that the proposed converter contains various superior qualities, such as the following:

- Three possible voltage gains. The theoretical maximum voltage gain of the converter can reach three G = 3 but it can also provide G = 2/-1 with common grounding,

- Low number of switches. The converter requires only two switches and four diodes, which

is favorable compared to different SC converters such as in [10] or [17],

M. Chojowski, R. Sosnowski, M. Baszyński

- The principle of operation assumes the transfer of energy through the capacitors. A tiny choke has been used to achieve a quasi-sinusoidal current in the circuits where the switched capacitors are charged and discharged,

- Low voltage stresses on switches and diodes. All elements' voltage stress is equal to input voltage (beside voltage overshoot),

- The efficiency was greater than 96% in the range from 120 W to 500 W (with the highest value  $\eta_{\text{max}} = 97.29\%$ ). Furthermore, the design can be improved with a focus on minimizing resistances.

#### References

- [1] Ioinovici A., Switched-capacitor power electronics circuits, IEEE Circuits Syst. Mag., vol. 1, no. 3, pp. 37–42 (2001), DOI: 10.1109/7384.963467.

- [2] Forouzesh M., Siwakoti Y.P., Gorji S.A., Blaabjerg F., Lehman B., *Step-Up DC–DC Converters: A Comprehensive Review of Voltage-Boosting Techniques, Topologies, and Applications*, IEEE Trans. Power Electron., vol. 32, pp. 9143–9178 (2017), DOI: 10.1109/TPEL.2017.2652318.

- [3] Waradzyn Z., Stala R., Mondzik A., Skała A., Penczek A., GaN-Based DC-DC Resonant Boost Converter with Very High Efficiency and Voltage Gain Control, Energies, vol. 13, no. 6403 (2020), DOI: 10.3390/en13236403.

- [4] Chojowski M., Stala R., Piłat A., Skowron M., Folmer S., The Design Concept of Low Cost and Volume Switched-capacitor DC–DC Resonant Converter, 2021 IEEE 19th International Power Electronics and Motion Control Conference (PEMC), Gliwice, Poland, pp. 200–206 (2021), DOI: 10.1109/ PEMC48073.2021.9432547.

- [5] Li S., Xie W., Smedley K.M., A Family of an Automatic Interleaved Dickson Switched-Capacitor Converter and Its ZVS Resonant Configuration, IEEE Transactions on Industrial Electronics, vol. 66, no. 1, pp. 255–264 (2019), DOI: 10.1109/TIE.2018.2829682.

- [6] Sun R.Y., Webb S., Liu Y.-F., Flying capacitor design considerations for a 48-to-12 V, 35 a split-phase Dickson SC converter, Chinese Journal of Electrical Engineering, vol. 6, no. 4, pp. 28–41 (2020), DOI: 10.23919/CJEE.2020.000028.

- [7] Alzahrani A., Shamsi P., Ferdowsi M., Analysis and design of bipolar Dickson DC–DC converter, 2017 IEEE Power and Energy Conference at Illinois (PECI), pp. 1–6 (2017), DOI: 10.1109/PECI. 2017.7935733.

- [8] Alzahrani A., Shamsi P., Ferdowsi M., Boost converter with bipolar Dickson voltage multiplier cells, 2017 IEEE 6th International Conference on Renewable Energy Research and Applications (ICRERA), pp. 228–233 (2017), DOI: 10.1109/ICRERA.2017.8191271.

- [9] Cao Y., Samavatian V., Kaskani K., Eshraghi H., A Novel Nonisolated Ultra-High-Voltage-Gain DC– DC Converter with Low Voltage Stress, IEEE Transactions on Industrial Electronics, vol. 64, no. 4, pp. 2809–2819 (2017), DOI: 10.1109/TIE.2016.2632681.

- [10] Stala R. et al., High-Gain Switched-Capacitor DC–DC Converter with Low Count of Switches and Low Voltage Stress of Switches, IEEE Access, vol. 9, pp. 114267–114281 (2021), DOI: 10.1109/AC-CESS.2021.3104399.

- [11] Law K.K., Cheng K.W.E., Yeung Y.P.B., *Design and analysis of switched-capacitor-based step-up resonant converters*, IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 52, no. 5, pp. 943–948 (2005), DOI: 10.1109/TCSI.2004.840482.

- [12] Li Z. et al., Analysis and Design of Half-bridge Dickson Resonant Switched-Capacitor Converters with "Indirect" Resonant Core, IEEE Transactions on Industry Applications, vol. 57, no. 5, pp. 5063–5073 (2021), DOI: 10.1109/TIA.2021.3091552.

- [13] Emadi A., Williamson S.S., Khaligh A., Power electronics intensive solutions for advanced electric, hybrid electric, and fuel cell vehicular power systems, IEEE Transactions on Power Electronics, vol. 21, no. 3, pp. 567-577 (2006), DOI: 10.1109/TPEL.2006.872378.

- [14] Wang J., Automotive Headlamp HID Ballast Reference Design Using the dsPIC®DSC Device, Microchip Technology Inc., AN1372 (2011-2012).

- [15] Lee M., Lai J.-S., Spread-Spectrum Frequency Modulation with Adaptive Three-Level Current Scheme to Improve EMI and Efficiency of Three-Level Boost DCM PFC, IEEE Transactions on Power Electronics, vol. 36, no. 3, pp. 2476–2480 (2021), DOI: 10.1109/TPEL.2020.3016238.

- [16] Fukuda K., Koizumi H., Three-level buck-boost dc-dc converter with voltage-lift-type switchedinductor, IECON 2013 - 39th Annual Conference of the IEEE Industrial Electronics Society, pp. 1368-1373 (2013), DOI: 10.1109/IECON.2013.6699332.

- [17] Emadi A. Williamson S.S., Khaligh A., Power electronics intensive solutions for advanced electric, hybrid electric, and fuel cell vehicular power systems, in IEEE Transactions on Power Electronics, vol. 1, no. 3, pp. 567-577 (2006), DOI: 10.1109/TPEL.2006.872378.

- [18] Kothapalli K.R., Ramteke M.R.R., Suryawanshi H.M., Reddi N.K., Kalahasthi R.B., Soft-Switched Ultra High Gain DC DC Converter with Voltage Multiplier Cell for DC Microgrid, in IEEE Transactions on Industrial Electronics (2020), DOI: 10.1109/TIE.2020.3031453.

- [19] Choi W.-Y., Yang M.-K., Soft-Switching Bidirectional Three-Level DC-DC Converter with Simple Auxiliary Circuit, Electronics, vol. 8, no. 983 (2019), DOI: 10.3390/electronics8090983.

- [20] Zulauf G., Park S., Liang W., Surakitbovorn K.N., Rivas-Davila J., COSS Losses in 600 V GaN Power Semiconductors in Soft-Switched, High- and Very-High-Frequency Power Converters, IEEE Transactions on Power Electronics, vol. 33, no. 12, pp. 10748–10763 (2018), DOI: 10.1109/TPEL. 2018.2800533.

- [21] Tektronix, Inc., TCP0030A Datasheet 30 A AC/DC Current Probe, online: https://www.tek.com/ datasheet/30-ac-dc-current-probe, accessed May 2022.

- [22] Tektronix, Inc., MDO3000 Mixed Domain Oscilloscope, online: https://www.tek.com/oscilloscope/ mdo3000-mixed-domain-oscilloscope, accessed May 2022.

- [23] Tektronix, Inc., TPP1000 Passive Voltage Probes, online: https://www.tek.com/datasheet/passivevoltage-probes, accessed May 2022.

- [24] YOKOGAWA, WT500 Power Analyzer, WT500 Power Analyzer datasheet, online: https://tmi.yoko gawa.com/solutions/products/power-analyzers, accessed May 2022.

- [25] Grandi G., Kazimierczuk M.K., Massarini A., Reggiani U., Sancineto G., Model of laminated iron-core inductors for high frequencies, IEEE Transactions on Magnetics, vol. 40, no. 4, pp. 1839–1845 (2004), DOI: 10.1109/TMAG.2004.830508.

- [26] CREE, Silicon Carbide Power MOSFET, C3M0060065D datasheet, online: https://assets.wolfspeed. com/uploads/2020/12/C3M0060065D.pdf, accessed May 2022.

- [27] VISHAY, Dual High Voltage Trench MOS Barrier Schottky Rectifier, VB60170G-E3, online: https: //www.vishay.com/docs/89950/vb60170g.pdf, accessed May 2022.