BULLETIN OF THE POLISH ACADEMY OF SCIENCES TECHNICAL SCIENCES DOI: 10.24425/bpasts.2024.150810

THIS IS AN EARLY ACCESS ARTICLE.

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication.

# Experimental evaluation of low-voltage DC/DC boost converters for renewable energy applications

Jakub Dawidziuk<sup>1</sup>, Michał Harasimczuk\*<sup>1</sup> and Rafał Kopacz<sup>2</sup>

<sup>1</sup> Faculty of Electrical Engineering, Bialystok University of Technology <sup>2</sup> Institute of Control and Industrial Electronics, Warsaw University of Technology

Abstract. The demand for energy in the world is growing, and the requirements for the efficiency of energy-saving technologies used in renewable energy sources, especially prominent in terms of power electronics, are also increasing. In many renewable energy applications, high-efficiency, high-power DC/DC converters are necessary as an interface between various low-voltage sources and higher output voltage loads, e.g., in photovoltaics. The article presents a comprehensive study on reducing power losses in electric energy conversion in modified isolated and non-isolated DC/DC boost converters powered by low-voltage energy sources. The main desirable features, such as high energy efficiency, high conversion ratio, and low stress on the switches and diodes, were compared and further experimentally validated. The experimental evaluation indicates that the highest efficiency of 96.7%, with a conversion ratio of more than 10, was achieved in the interleaved boost-flyback DC/DC converter. Other investigated systems, namely non-isolated push-pull-boost converters, isolated half-bridge boost, and partially parallel boost converters, achieved slightly lower efficiency. Simultaneously, using the suggested topology, the passive component count was reduced. Furthermore, better utilization of switches and a higher conversion ratio are provided, as well as a possibility of working at a lower duty cycle compared to other step-up converter topologies. All in all, the proposed and studied converters exhibit certain advantages over other state-of-the-art solutions and thus can be competitively and effectively employed in modern low-voltage DC/DC applications such as photovoltaics.

**Keywords:** renewable energy, boost DC/DC converters, high-efficiency converters, current-fed converters.

## 1. INTRODUCTION

Electricity is the noblest and the most common energy carrier, and saving it through low-loss transmission has become a serious challenge for our civilization. Furthermore, recent environmental issues have accelerated the use of a more eco-friendly option in the form of renewable energy sources (RES), e.g., photovoltaics. Optimizing the use of RES to produce electrical energy is one of the possible solutions that can help save exhaustible fossil-based energy resources.

In modern technologies, most of the electricity is transformed, and the system that adjusts the form of electricity to the needs of the recipient is a power electronic converter, often a DC/DC power supply. Switch-mode power conversion, founded on pulse width modulated (PWM) converters, has for many years been a basis of modern electronics in many sectors, including utility, industrial, commercial, and consumer markets.

\*e-mail: m.harasimczuk@pb.edu.pl

In practice, the output voltage of RES systems, such as photovoltaic modules, fuel cells, or batteries, are of the order of (12-50) V. To connect such systems to the domestic or industrial loads or the main grid (230 V), usually via a single-phase inverter, the DC output voltage has to be stepped up to around (350-400) V [1]. Furthermore, the performance of the energy conversion system comprising a low voltage power source, DC/DC converter and inverter module is mainly governed by the efficiency of the used power electronic technologies. Thus, low power loss converter topologies are required.

In a basic non-isolated DC/DC boost converter, it is not possible to achieve high voltage gain (>10), high power, and high switching frequency at the same time for several reasons. Firstly, to achieve high voltage gain, the transistor must be controlled with a high duty ratio, which increases its conduction losses. Secondly, with high output voltage, a transistor with high voltage ratings resulting in high drain-source resistances is needed, which additionally increases its power losses. Finally, the reverse recovery current of the output diode, while turning on the transistor, increases the

switching losses and limits the switching frequency. Reverse recovery current could be eliminated in discontinuous conduction mode (DCM); however, deformed current components increase their conduction losses, limiting the maximum output power. Therefore, many different solutions have been developed to ensure a high voltage gain. The most important ones are based on various techniques such as voltage multiplier cells, coupled inductors, or circuits utilizing the transformer turn ratio. However, these are a source of other issues such as high component count and extra losses caused by the leakage inductance. Moreover, an interesting solution is to employ converters utilizing the switched capacitor technique and coupled inductors in a common circuit. Such an approach enables achieving high switching frequencies, limited losses due to recovering energy from the leakage inductance, and the possibility of obtaining a high voltage gain. However, such converters are only capable of achieving high efficiency at low output power, typically not exceeding 300 W [2]. All in all, a myriad of converters have been presented in the literature [3]. Each topology has its own advantages and disadvantages and should be selected based on the application and its requirements, e.g., isolated/non-isolated, unidirectional/bi-directional, voltage-fed/current-fed, hard/soft switched, and more.

To reduce losses, size and cost, non-isolated DC/DC converter topologies [3] are preferred in low and mediumpower applications over their isolated counterparts, which use a transformer to achieve the required voltage gain. However, for obvious reasons, such systems cannot be employed in applications that require galvanic insulation. On the other hand, when such a feature is not required, a high voltage conversion ratio can be achieved by using converters with tapped inductors and quasi-resonant circuits, ensuring soft switching of converter components [4-6]. There have been several state-of-the-art concepts presented that study improved non-isolated boost converters. In [6-8], new single-switch topologies were proposed. The main advantage of such systems is the simplistic control, as only one device has to be driven, and the proper operation is assured through passive components, e.g., in the form of resonant tanks. However, such converters usually require high utilization of the transistors, leading to increased conduction losses. Twoswitch structures were also studied to merge several voltage-boosting stages [9-15], which allow for the achievement of higher voltage gain with lower duty, lower losses, and higher efficiencies. On the other hand, with the increased number of transistors, the systems become more complex, and their base cost is increased. Simultaneously, novel, highly-performant isolated structures are also introduced [16], specifically prominent for applications that require additional safety assurance, e.g., battery energy storage systems. These are usually characterized by lower efficiencies compared to non-isolated counterparts as a result of increased semiconductor component count and the inclusion of a transformer. However, despite the fact that the discussed isolated and non-isolated structures are simple

and effective, their maximum output power usually does not exceed hundreds of watts.

The literature includes the results of scientific research and design solutions of DC/DC converters achieving high conversion ratio values or high energy conversion efficiency, even exceeding 95%. However, there are only a few solutions that combine both of these features in applications for the conversion of electric power above 1 kW, which are of great significance in a rapidly growing RES market, e.g., in residential photovoltaics and extended use of battery energy storage systems. Furthermore, parallel-connection of photovoltaic panels [9, 10], often advantageous compared to more conventional seriesconnection, for example when shading is considered [11] necessitates higher power converters with very low input voltage. Thus, there is a great need to find new solutions to increase the converters' voltage gain, power density, and efficiency and/or lower the cost [12-14] with increased power range, which is the subject of consideration in this work [5, 6, 12-15, 17-21].

Based on the comparison of the physical parameters of several hundred converters from the literature, a few systems were selected according to the established criteria, and then experimental tests were carried out on modified isolated and non-isolated DC/DC converters [12, 13]. Furthermore, this includes the proposal of new power converter topologies. The selection process included efficiency ( $\eta_{\text{max}} \ge 94\%$ ), input voltage ( $V_i \le 50 \text{ V}$ ), power ( $P_o \ge 1 \text{ kW}$ ), voltage conversion ratio ( $B \ge 10$ ), switching frequency, converter complexity, estimated cost, size, and weight.

The paper is constructed as follows. After the concise introduction showcasing the importance of highly-performant boost DC/DC converters, Section 2 investigates isolated boost topologies, while Section 3 studies non-isolated structures. In both cases, the analysis is founded on theoretical considerations as well as experimental evaluation. Finally, the findings are discussed and concluded in the last Section 4.

# 2. ISOLATED INDUCTOR-FED DC/DC BOOST CONVERTERS

The article proposes two improved isolated power converters with high conversion ratio and high efficiency. converter configurations were investigated theoretically, and the constructed prototypes were tested in laboratory conditions. The comparison has been made taking into consideration the important descriptive equations of voltage conversion ratio, transformer turns ratio, the inductor current ripple, switching frequency, the maximum duty cycle for minimum input voltage, voltage stress over transistors and diodes, and ripple voltage of output filter capacitors, for three isolated converters. Ideal converter components were adopted to simplify the theoretical analysis.

In the following, the analysis will involve significant loss factors involved when using power MOSFETs as primary switches in high-power, low-voltage converters. Due to the very high input current, primary switch conduction losses are dominant. Two quantities determine the switch

**TABLE 1.** Relationships for the conventional dual inductor converter

| Specification                                              | Isolated dual inductor-fed                                                                                       |      |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------|

| Voltage conversion ratio $V_o/V_i$                         | $\frac{2n}{1-D}$                                                                                                 | (4)  |

| Switch peak current $I_{S,pk}$                             | $I_{i} = \frac{2nI_{o}}{1 - D}$                                                                                  | (5)  |

| Diode peak current $I_{D,pk}$                              | $\frac{I_{\rm i}}{n} = \frac{2I_{\rm o}}{1 - D}$                                                                 | (6)  |

| Diode average current $I_{D,av}$                           | $I_{D,av} = \frac{I_i}{2n} (1 - D) = I_o$                                                                        | (7)  |

| Inductor dc and rms currents $I_{L,dc}$ ; $I_{L,rms}$      | $\frac{I_{\rm i}}{2} = \frac{nI_{\rm o}}{1 - D}$                                                                 | (8)  |

| Capacitor rms current $I_{\text{C,rms}}$                   | $\frac{I_{\rm i}}{n} \sqrt{\frac{1}{2} - \frac{D}{2}} = I_{\rm o} \sqrt{\frac{2}{1 - D}}$                        | (9)  |

| Voltage switch $V_{S,max}$                                 | $\frac{V_{i}}{1-D} = \frac{V_{o}}{2n}$                                                                           | (10) |

| Inductance of input inductor $L_1=L_2$                     | $\frac{V_{\rm i}D}{4\Delta I_{\rm i}f_{\rm S}} = \frac{V_{\rm o}D(1-D)}{8n\Delta I_{\rm i}f_{\rm S}}$            | (11) |

| Capacitance of capacitors $C_1=C_2$                        | $\frac{I_{i}(2D-1)}{4nf_{s}\Delta V_{o}} = \frac{I_{o}(2D-1)}{2(1-D)f_{s}\Delta V_{o}}$                          | (12) |

| Primary rms transformer voltage $V_{\text{Tr.p.rms}}$      | $V_{i}\sqrt{\frac{2}{1-D}} = \frac{V_{o}}{n}\sqrt{\frac{1-D}{2}}$                                                | (13) |

| Secondary rms<br>transformer voltage $V_{\text{Tr,s,rms}}$ | $nV_{i}\sqrt{\frac{2}{1-D}} = V_{0}\sqrt{\frac{1-D}{2}}$                                                         | (14) |

| Primary rms transformer current $I_{\text{Tr,p,ms}}$       | $\frac{I_{\rm i}}{2}\sqrt{1-D} = nI_{\rm o}\sqrt{\frac{1}{1-D}}$                                                 | (15) |

| MOSFET conduction losses $P_{\text{MOSFET}}$               | $R_{\text{DS,on}} \left( \frac{3}{4} - \frac{D}{2} \right) \left( \frac{P_1}{V_i} \right)^2$                     | (16) |

| Diode conduction loss $P_{D,con}$                          | $\frac{P_{\rm o}}{V_{\rm o}}V_{\rm D} + R_{\rm D}\left(1 - D\right)\left(\frac{P_{\rm o}}{2nV_{\rm i}}\right)^2$ | (17) |

conduction losses – switch rms current,  $I_{S,rms}$ , and switch on-resistance,  $R_{DS,on}$ . Switch rms current is a function of the selected converter topology and its output power. The efficiency of energy conversion in the converter depends, above all, on the topology of the converter, the technology of semiconductors and magnetic components, voltage values in the DC circuit, and the applied control methods. Currently, Silicon power MOSFETs constitute the best available technology for low voltage switches, as they converge satisfactory performance with minimal cost.

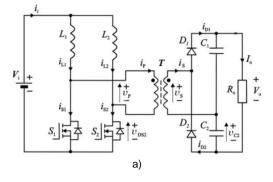

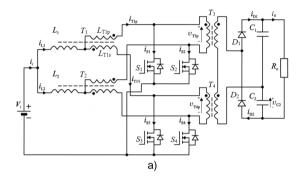

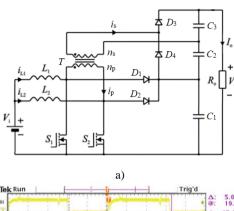

A. Isolated dual inductor-fed DC/DC boost converter Among the various current-fed boost topologies, a dual inductor-fed boost converter (Fig. 1a) is a reasonable solution due to its higher voltage conversion ratio, less stress on the power switches, and lower conduction losses compared to a basic converter with a single inductor. To maximize the voltage conversion ratio of the converter, the output side of the circuit is configured as a voltage doubler rectifier that consists of boost rectifiers  $D_1$  and  $D_2$  and output filter capacitors  $C_1$  and  $C_2$  connected across load  $R_0$ . The main feature of this circuit is that the voltage stress of each switch is half the voltage stress of the switches in the

Fig.1. Isolated dual inductor-fed boost converter: a) circuit diagram, b) theoretical waveforms for steady-state operation.

single inductor implementation. Additionally, the input current is distributed evenly through two boost inductors so that the current ripple in the output capacitor is smaller than in the single-inductor implementation. The need for two magnetic components is offset by the fact that each inductor carries half of the input current (Fig. lb).

So far, in scientific literature, the average and rms current values in the converter elements have not been exhaustively described, allowing for the calculation of conduction losses. Simultaneously, their calculation is essential from the perspective of optimally designing the converter along with its cooling system. These quantities have been described by equations (1) - (17) depicted in Table 1. In addition to the conduction losses, the total losses are also affected by the switching losses, which increase with the switching frequency and the transistor technology used [22]. Note that the extensive description for dual inductor-fed converter as shown in Table 1, has not been presented before. However, such equations have been already provided for the rest of the considered systems, and thus are not included in the paper.

The rms current flowing in the switches in an isolated boost converter can be expressed as

$$I_{\text{S,rms}} = I_{\text{i}} \sqrt{\frac{3}{4} - \frac{D}{2}} \sqrt{1 + \frac{1}{3} \left(\frac{\Delta i_{\text{L}}}{2I_{\text{i}}}\right)^{2}}$$

(1)

where:  $I_i$  - average input current, D - switch duty cycle,  $\Delta i_L$  - inductor current ripple.

If the inductor ripple current is much smaller than the dc input current,  $\Delta i_L \ll I_i$  constant inductor current during one switching period can be assumed, then the switch rms current becomes approximately

$$I_{\text{S,rms}} \approx I_{\text{i}} \sqrt{\frac{3}{4} - \frac{D}{2}} = \frac{P_o}{V_i} \sqrt{\frac{3}{4} - \frac{D}{2}}$$

, (2)

where:  $V_i$  and  $P_o$  are the input voltage and output power, respectively.

In an isolated boost converter with voltage doubler output, the corresponding diode rms current is equal to

$$I_{\rm D,rms} = \frac{I_{\rm i}}{2n} \sqrt{1 - D} \sqrt{1 + \frac{1}{3} \left(\frac{\Delta i_{\rm L}}{2I_{\rm i}}\right)^2} \approx \frac{I_{\rm i}}{2n} \sqrt{1 - D} \ .$$

(3)

where  $n=N_{\rm S}/N_{\rm P}$  is the transformer turns ratio. However, leakage of inductance energy in the transformer causes high voltage spikes on the switches and diodes, reducing the converter efficiency. The remaining equations describing the operation of the converter have been included in Table 1, taking into account the assumption that the inductor current in one converter period is constant.

Hence, to achieve good performance, the circuit techniques must focus on the voltage conversion ratio and also to clamp the voltage spikes [15, 16]. Moreover, a soft start-up is not possible due to the limited range of duty cycle above 0.5. For empirical verification of the theoretical relationships, the components of the dual inductor-fed boost converter prototype, presented in Table 2, were used for testing. Topology verification was performed by testing the prototype converter in the power range (100-1400) W and input voltages (10-40) V.

TABLE 2. Components of the prototype dual inductor-fed boost converter

| Component                     | Type            | Specification                    |

|-------------------------------|-----------------|----------------------------------|

| Input inductors $L_1$ , $L_2$ | EMS-0552825-060 | 70 uH /40 A                      |

| Switches $S_1$ , $S_2$        | IRFP4668        | $200~V/130~A/8~m\Omega$          |

| Diodes $D_1$ - $D_4$          | STPSC10H12      | 1200 V/10 A/1.35 V               |

| Capacitors $C_1$ - $C_3$      | PCPW245         | $22~\mu F/700~V$                 |

| Transformer $T$               | T250DC          | $N_{\rm p}/N_{\rm s}=8/16$ turns |

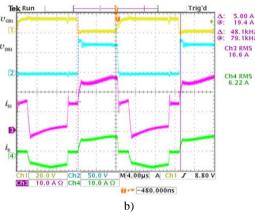

**Fig.2.** Experimental waveforms of the isolated dual-inductor current-fed boost converter: a)  $v_{GS1}$ ,  $v_{GS2}$  – gate-to-source voltages,  $i_{S1}$  – transistor  $S_1$  drain current,  $v_{DS1}$ - transistor  $S_1$  drain-to-source voltage, b)  $i_{L1}$ ,  $i_{L2}$  – inductor  $L_1$  and  $L_2$  current,  $v_{Ts}$ – voltage across the secondary winding of the transformer

Figure 2 shows the waveforms of the isolated dual inductorfed boost converter at the main operating region. The duty cycle higher than 0.54 is necessary to achieve the required output voltage, which results in serious voltage overshoots (about 30 V) during turn-off. By employing snubber circuits, the voltage spike can be reduced. Unfortunately, this comes at the expense of efficiency. The experimental waveforms (Fig. 2) are similar to the theoretical ones (Fig. 1b) with the expected differences reflecting the use of real devices. The dual inductor-fed boost converter constitutes a benchmark for the comparison with insulated converter described below -half-bridge and partially parallel

## B. Isolated half-bridge DC/DC boost converter

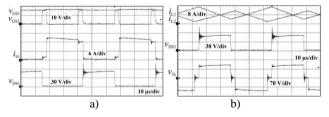

Current-fed, full-bridge and half-bridge converters are a good solution for high power and high step-up conversion. The isolated half-bridge current-fed DC/DC converter topology [12] is shown in Fig. 3. The half-bridge structure combines some features of high efficiency and a small number of semiconductor components. The voltage conversion ratio of the half-bridge converter is B = 2n/(1-D). The converter is supplied by a single input inductor L, integrated and magnetically coupled with the balancing transformer  $T_1$ . Integration of the inductor with the balancing transformer by core sharing reduces the number of magnetic cores and suppresses flux ripple. The use of both planar technology and integrated magnetics ensures higher efficiency of the converter when compared with similar solutions within this power range. The DC/AC and AC/DC circuits are connected by the isolation transformer  $T_2$  with a step-up turns ratio (1:n). Replacing the rectifier bridge in the DC output circuit with a voltage doubler reduces the transformer turns ratio  $T_2$ , the size of the

**Fig.3.** Experimental waveforms of the isolated half-bridge DC/DC boost converter: a) circuit, b)  $v_{GS1}$ ,  $v_{GS2}$  – gate-to-source voltages,  $i_{S1}$  – transistor  $S_1$  drain current,  $v_{DS1}$ - transistor  $S_1$  drain-to-source voltage, c)  $i_L$  – input current,  $v_{Tp2}$  – voltage across the primary winding of the transformer,  $i_{D1}$  – diode  $D_1$  current.

91

0

250

500

transformer, which consequently reduces the leakage inductance. Additionally, by interleaving the planar transformer windings, leakage inductance can be significantly reduced, which helps in reducing voltage overshoots during transistor turn-off. Owing to the implementation of an isolation transformer into the converter structure, the DC/DC stage provides not only voltage step-up but also galvanic isolation. This adaptation provides reconfiguration flexibility and helps to meet the safety standards of the power conversion system.

To verify the operation principle of the proposed converter, a laboratory prototype was assembled and tested. The specifications and parameters of the converter are given in Table 3. Losses in the converter are the sum of losses in the semiconductor and passive elements. The balance of losses in the magnetic elements was calculated for a given operating point, and in the isolation transformer, additional AC losses at non-sinusoidal current were estimated. Furthermore, given the low impact on power losses compared to other loss sources, the capacitor ESR losses have been omitted. The balance of losses was carried out for the supply voltage  $(25 \div 50)$  V, the duty cycle D = 0.54, and the load resistance  $R_0 = 120 \Omega$ . Power losses in dynamic states of MOSFET switches were measured with an oscilloscope equipped with a specialized DPOPWR application by Tektronix. Theoretical calculations of losses in diodes were verified on the basis of the measured effective and average current values. Losses in series resistance ESR of output capacitors were not taken into account due to their small share (about 0.1 W) in the power losses. The converter operated with a duty cycle of less than 0.8, obtaining 350 V of the output voltage. In the (30-40) V supply voltage range, increasing the input voltage by 5 V increased the efficiency by about 1% (93.5%, 94.5%, 95.5%, respectively).

TABLE 3. Isolated half-bridge boost converter components

| Output power $P_0 = (200-1500)$ W                | Component                    | Туре                  | Specification                                              |

|--------------------------------------------------|------------------------------|-----------------------|------------------------------------------------------------|

| Input voltage $V_i = (24-50) \text{ V}$          | Inductor L                   | Integrated with $T_1$ | 12 μΗ                                                      |

| Max. input current $I_{i(max)} = 62.5 \text{ A}$ | Switches $S_1, S_2$          | IRFP4568              | 150 V/171 A/5.9 mΩ                                         |

| Input current ripple $\Delta I_{i(\%)} < 30\%$   | Diodes $D_1, D_2$            | STPSC10<br>H12        | 1200 V/10 A/1.35 V                                         |

| Output voltage $V_0 = 350 \text{ V}$             | Capacitors $C_1$ , $C_2$     | PCPW245               | $60~\mu F/700~V$                                           |

| Efficiency $\eta > 95\%$                         | Transf $T_1$<br>Transf $T_2$ | T1000DC<br>T250DC     | $N_p=N_s=8 \text{ turns}$<br>$N_p=8, N_s=16 \text{ turns}$ |

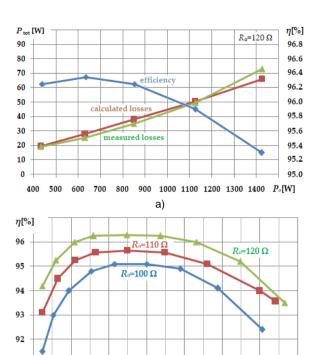

In the range of input voltages (25-50) V, losses in semiconductor devices constitute about 79% of total losses in the entire transformed power range. The source of the rest of the calculated losses lies in the magnetic component. Figure 4a) shows the comparison of the calculated (on the basis of [12]) and measured total losses and the efficiency of the converter depending on the input power. In the power range of (400-1500) W, 90% accuracy of the analytical

**Fig. 4.** Experimental research results at duty cycle D = 0.54: a) total converter losses  $P_{tot}$  and efficiency η as a function of output power  $P_o$  at load resistance  $R_o$  = 120 Ω, b) efficiency η as a function of output power  $P_o$  at load resistances  $R_o$  = (100, 110, 120) Ω.

b)

750

1000

1250

1500

$P_o[W]$

determination of losses was achieved. For the calculation of losses, both conduction losses and switching losses were taken into account. The slight difference between the results of experimental studies and calculations indicates the high quality of the loss model in the converter.

As can be seen in Fig. 4b), the converter maintains an efficiency of over 91.5% for the whole power range, and for the scope (200-1300) W, the converter efficiency was above 94%, reaching the maximum value of 96.3% for 600 W of processed power. The power losses of the converter are depicted in Table 4.

TABLE 4. Total losses of the half-bridge boost converter

| $V_{\rm i}$ | $P_{ m semicond}$ | $P_{\mathrm{magnet}}$ | $P_{ m total}$ |

|-------------|-------------------|-----------------------|----------------|

| [V]         | [W]               | [W]                   | [W]            |

| 25          | 15.54             | 4.24                  | 19.78          |

| 30          | 23.71             | 6.26                  | 29.97          |

| 35          | 31.15             | 8.58                  | 39.74          |

| 40          | 41.30             | 11.29                 | 52.59          |

| 45          | 52.22             | 14.39                 | 66.60          |

| 50          | 64.88             | 17.82                 | 82.70          |

The results of the experimental tests document the effectiveness of the parallel operation of the boost circuits sharing one input inductor. This solution enables a peak efficiency above 96%, a conversion ratio of more than 10, with a design output power of about 1 kW.

As a result of using the proposed topology and construction of magnetic elements, a high-voltage conversion ratio was obtained, with only double the transformer ratio, which benefited from the limitation of voltage overshoots caused

by the transformer leakage inductance. The obtained parameters prove the high performance of the isolated halfbridge converter.

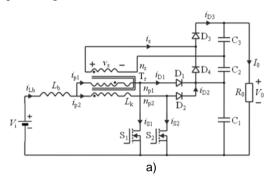

C. Isolated partially parallel two-inductor-boost converter

It is commonly known that in converters powered by a low-voltage energy source, obtaining a high voltage conversion ratio (output voltage) requires a high transformer turns ratio. Although it is a simple method to achieve a high conversion ratio, it does not always give the target end result, i.e., high efficiency of the converter. However, a parallel connection of two or more isolated converters reduces both the transformer ratio and losses in the power switches.

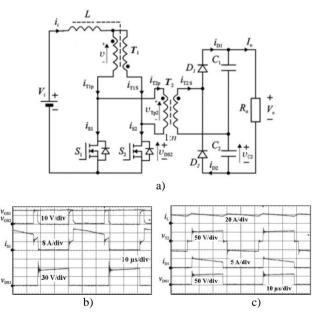

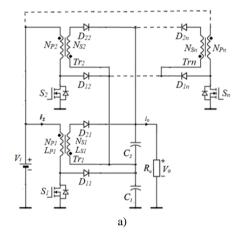

The proposed isolated partially parallel two-inductor-boost with a voltage doubler converter in Fig. 5a is characterized by high efficiency and high conversion ratio. The

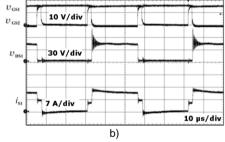

**Fig. 5.** Isolated partially parallel two-inductor-boost converter and test results with load resistance  $R_o$ =180 Ω: a) circuit; b)  $v_{GS1}$ ,  $v_{GS2}$  - gate-to-source voltages,  $v_{DS1}$  - transistor  $S_1$  drain-to-source voltage,  $i_{S1}$  - transistor  $S_1$  drain current, c) an example of the operating point of the converter  $V_i = U_{dc1}$ ,  $I_i = I_{dc1}$ ,  $P_i = P_1$ ,  $V_o = U_{dc2}$ ,  $I_o = I_{dc2}$ ,  $P_o = P_2$ ,  $η = η_1$

transformer turns ratio can be reduced by half due to its partially parallel connection.

The use of balancing transformers allows for an even distribution of the input current among all of the converter transistors. As the input voltage is in the range of tens of volts, transistors with low drain-source resistance can be applied to the structure. Extension to higher numbers of paralleled converters is possible by adding an extra current transformer for each extra paralleled power stage. In general, *N*-1 current balancing transformers are needed for paralleling *N* power stages.

The operation cycles of the partially parallel and half-bridge converter are analogous. This is why the shapes of the waveforms are the same; only the instantaneous values of voltages and currents differ.

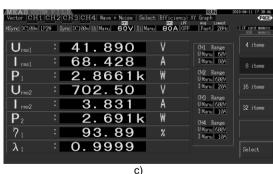

Since a partially parallel converter is a parallel connection of two half-bridge converters, its voltage conversation ratio is twice as high as in the half-bridge converter and is equal to B = 4n / (1-D). In order to verify the operation principle of the proposed converter, a laboratory prototype was assembled and tested. The specifications and parameters of the converter are given in Table 5. As the designed power of the partially parallel converter prototype was twice as high as in the half-bridge converter, twice as many identical magnetic elements were used for its construction as in the half-bridge converter. One of the test results in the form of voltage and current oscillograms and indications of the power analyzer HIOKI 3390 at the selected operating point is shown in figures 5b and 5c, respectively. The experimental waveforms of the drain-source voltage  $v_{DS1}$ and the current  $i_{S1}$  (Fig. 5b) are similar in shape to the theoretical waveforms and to the corresponding waveforms of the two converters presented above.

The tests show that with a minimum input voltage of 24 V, a duty cycle of 0.54 and the transformer ratio n=2, the system is capable of achieving an output voltage of over 350 V and an efficiency of 95.7% at an input power of 925 W. During the converter operation with an input voltage of 42 V, a duty cycle of 0.54, an input power of 2866 W, an efficiency of 93.9% was obtained, and an output voltage of over 700 V.

TABLE 5. Parameters and specification of the partially parallel converter components

| Output power $P_0 = (200-3000) \text{ W}$          | 1 Component Type       |                            | Specification                         |  |  |

|----------------------------------------------------|------------------------|----------------------------|---------------------------------------|--|--|

| Input voltage $V_i$ = (24-50) V                    | Inductors $L_1, L_2$   | Integrated with $T_1, T_2$ | 22 μΗ                                 |  |  |

| Max. input current $I_{i(max)} = 62.5 \text{ A}$   | Switches $S_1$ - $S_4$ | IRFP4568                   | 150 V/171 A<br>/5.9 mΩ                |  |  |

| Input current ripple $\Delta I_{i(\%)} < 30\%$     | Diodes $D_1, D_2$      | STPSC10H12                 | 1200 V/<br>10 A/1.35 V                |  |  |

| Output voltage $V_0 = 350 \text{ V}/700 \text{ V}$ | Capacitors $C_1, C_2$  | PCPW245                    | $60~\mu\text{F}/700~V$                |  |  |

| Ecc                                                | Transf. $T_1, T_2$     | Integrated                 | $N_p = N_s = 8$ turns                 |  |  |

| Efficiency $\eta > 95\%$                           | Transf. $T_3$ , $T_4$  | with $L_1, L_2$<br>Planar  | $N_{\rm p}$ =8, $N_{\rm s}$ =16 turns |  |  |

D. Comparison of the isolated DC/DC boost converters The prototypes of the isolated converters were developed to validate the theoretical assumptions. The same elements were used to build the prototypes. Laboratory tests were carried out for the same range of input voltages, duty cycle, and switching frequency. The use of a voltage doubler simplifies obtaining 350 V (or higher) on a load with a duty cycle of about 0.6 over the range of input voltage changes (30 - 40) V. In order to reduce switching losses in the general balance of energy losses,  $f_s = 20 \text{ kHz}$  was adopted. The transient processes were tested with the Tektronix DPO5034 oscilloscope, while the efficiency input/output values of currents and voltages were measured with the HIOKI 3390 power analyzer. The source of the energy supplied to the converters was the MAGNA-POWER ELECTRONICS XR-50-100 power supply.

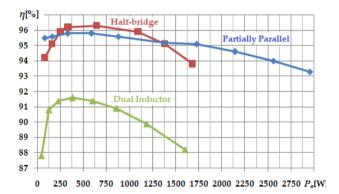

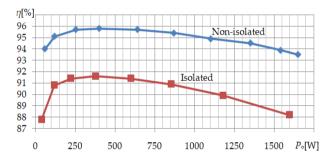

Figure 6 shows the efficiency characteristics as a function of the output power of three topologies described above: dual inductor-fed, half-bridge, and partially parallel isolated DC/DC boost converters measured for a constant duty cycle. D = 0.54 constant input voltage  $V_{in} = 24V$  and different load resistance, which results in different output power Po. The highest peak efficiency of 96.3% was achieved by the half-bridge converter. In this converter, in the range of the designed output power (200-1500) W, the efficiency exceeded 94.5%, while in the range (250-1100) W, which is 65% of the designed power, the efficiency was higher than 96%. A relatively flat characteristic was obtained during the tests of a partially parallel converter, which in the power range (80-1800 W) had an efficiency of over 95%, with a peak efficiency of 95.8%. For maximum power (3000 W), the efficiency decreased to 93.3%. This

**Fig. 6.** Measured efficiency  $\eta$  of isolated boost converters as a function of output power P<sub>o</sub>, D=0.54, V<sub>in</sub>=24 V

TABLE 6. List of basic parameters of the tested isolated converters

| Conver.                  | η    | $P_{o(max)}$ | $V_{\mathrm{o}}$ | $B_{ m meas}$ | $B_{ m theoret}$ | S | D |

|--------------------------|------|--------------|------------------|---------------|------------------|---|---|

| -                        | [%]  | [W]          | [V]              | [V/V]         | [V/V]            | - | - |

| Dual<br>inductor-<br>fed | 91.6 | 350          | 370              | 8,1           | $\frac{2n}{1-D}$ | 2 | 2 |

| Half-bridge              | 96.3 | 630          | 400              | 9,5           | $\frac{2n}{1-D}$ | 2 | 2 |

| Partially parallel       | 95.8 | 610          | 700              | 16,7          | $\frac{4n}{1-D}$ | 4 | 2 |

$V_i$ =42 V,  $f_s$ =19.5 kHz, S - number of transistors, D - number of diodes

converter generated an output voltage of 400 V and a power of 2866 W even at the input voltage of 24 V, the duty cycle factor D = 0.54, and the low transformer ratio of n = 2.

Increasing the input voltage to 42 V allows for a voltage higher than 700 V at the output of the converter and ensures the possibility of cooperation with a 3-phase DC/AC inverter. The energy transfer efficiency was 93.9%. The dual inductor-fed converter achieves a maximum efficiency of 91.6% with an output power of about 350 W. In the power range of (100-1150) W, the efficiency of the isolated converter is higher than 90%. This topology has a low voltage conversion ratio as it obtains B=10 with a duty cycle of D=0.9 and B=5.6 for D=0.54.

Table 6 presents the most important features of discussed isolated converters obtained as a result of laboratory tests. The proposed topologies, i.e., the half-bridge and the partially parallel one, are a modification of the dual inductor-fed converter. Here, the two input inductors have been replaced by an integrated inductor magnetically coupled with the balancing transformer. The novel converters showed about 4% higher efficiency than the classic dual inductor-fed converter. Proposed isolated boost converters achieve high efficiency and voltage gain at low duty cycles, making them suitable for use in the interface system of low-voltage, high-power supply with the power grid.

# 3. NON-ISOLATED INDUCTOR-FED DC/DC BOOST CONVERTERS

Most current-fed type boost topologies, including dualinductor schemes have major drawbacks. When a switch is turned off, high voltage oscillation between drain and source occurs due to the resonance between the transformer's leakage inductance and the switch's output capacitance. Another problem emerges when two switches are turned off simultaneously and high voltage spikes appear at the clamps of the inductors, and the switching devices would be permanently damaged. Therefore, the duty cycle of current-powered boost converters should be greater than 0.5.

High output voltage raises another problem. An abrupt start-up with a duty cycle larger than 0.5 gives rise to an excessive in-rush current at the converter input. This demands that switching devices with higher current ratings are required under normal operating conditions.

Some problems can be eliminated in the non-isolated converters presented below.

# A. Non-isolated dual inductor-fed DC/DC boost converter

By adding two diodes  $(D_1, D_2)$  and one output capacitor  $(C_1)$  to the isolated inductor-fed boost converter, a higher voltage conversion ratio, soft start-up, and reduction of the switch's turn-off voltage spike can be achieved in the non-isolated dual inductor-fed boost converter, as shown in Fig 7a). As both non/isolated dual inductor-fed boost converters have common roots, their operation cycles are analogous; their waveform shapes are the same, only the instantaneous voltages and currents differ (Fig. 2 and Fig. 7.b).

Since this topology combines a two-phase boost converter and a dual inductor-fed boost converter, the voltage

Fig. 7. Non-isolated dual inductor-fed boost converter: a) circuit, b)  $v_{GS1}$  – gate-to-source voltage,  $v_{DS1}$  – drain-to-source voltage,  $i_{S1}$  – drain current,  $i_{S}$  – secondary current through the transformer ( $V_i$ =31 V,  $I_i$ =37 A,  $v_{DS1}$ , max = 95 V,  $V_o$  = 373 V, D =0.6, B = 12)

conversion ratio rises to value B=(1+2n)/(1-D); hence, component stresses and switch conduction losses are reduced. In order to verify the operation principle of the proposed converter, a laboratory prototype was assembled and tested. The specifications and parameters of the laboratory prototype of a non-isolated dual inductor-fed converter are shown in Table 7.

Taking into account the waveform of switch voltage (e.g.  $v_{\rm DS1}$  on Fig. 7b), it can be shown that the converter has properties of self-clamping of the voltage. The voltage level across the switch  $S_1$  is reduced to the level on the capacitor  $C_1$ . The average currents of each output capacitor are the same at a steady state regardless of the duty cycle owing to the series connection. The average forward currents of diodes  $D_1$  and  $D_2$  are equal to half of the output DC current because these diodes are connected in parallel. The average

**TABLE 7.** Main specifications and components of the non-isolated dual inductor-fed DC/DC boost converter prototype

| Description              | Values                                                             |

|--------------------------|--------------------------------------------------------------------|

| Input voltage            | (9-31) V                                                           |

| Output voltage           | (110-380) V                                                        |

| Switching frequency      | 48 kHz                                                             |

| Switches $S_1$ and $S_2$ | IRFP4668PBF                                                        |

|                          | $(200 \text{ V}/130\text{A}/8\text{m}\Omega)$                      |

| Diodes $D_I$ - $D_4$     | C2D20120D (1200 V/20 A/1.6 V)                                      |

| Capacitor $C_I$          | $10 \mu\text{F}/350 \text{V}/4.8 \text{m}\Omega \text{MKP VISHAY}$ |

| Capacitors $C_2$ - $C_3$ | 470 μF/400 V/130mΩ electrolytic                                    |

| Inductors $L_1=L_2$      | DTMSS-47/0.068/45, 20 turns                                        |

| Transformer T            | Payton Planar P.N.56960/1000DC-8/16,                               |

|                          | n=2                                                                |

forward current of diodes  $D_3$  and  $D_4$  is equal to the output DC current  $I_0$ .

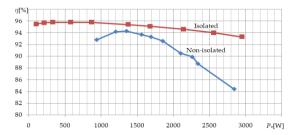

As before, with isolated converters, the non-isolated converter is compared to the dual inductor-fed boost converter. Figure 8 shows the efficiency comparison of non-isolated and isolated dual inductor-fed DC/DC boost converters within the range between (40-1650) W of output power at the switching frequency  $f_s = 20 \text{ kHz}$  (isolated) and  $f_s = 48 \text{ kHz}$  (non-isolated), duty cycle D = 0.6, input voltage  $V_i = 31 \text{ V}$ ,  $V_o = 373 \text{ V}$  (the voltage was equal to 373 V as the power was changed via variable load with constant duty cycle). Both converters achieve maximum efficiency at an output power of about 400 W, non-isolated 95.8% and isolated 91.6%. In the power range of (120-1100) W, the efficiency of the non-isolated converter exceeds 95%, and that of the isolated converter exceeds 90%. The nonisolated converter has a flatter efficiency curve rather than the isolated circuit. This characteristic shape results from the additional energy recovery circuit of the non-insulated converter. The voltage conversion ratio of the non-isolated topology is (1+2n)/(1-D) (1+2n)/2n times higher in comparison with the isolated boost topology. The measurements indicate that the use of the isolated converter can enable a high conversion ratio without the necessity to work at the highest duty cycle ( $D = 0.7 \rightarrow B = 10.4$ ).

**Fig. 8.** Measured efficiency  $\eta$  of dual inductor fed non-isolated and isolated boost converters as a function of output power P<sub>o</sub>, D=0.6

## B. Current-fed push-pull DC/DC boost converter

In high-voltage step-up systems supplied from a low-voltage source, it is crucial to provide a required level of voltage with high efficiency in the expected power range. Isolated current-fed converters, such as push-pull, bridge, and half-bridge converters, are effective in applications requiring a higher voltage conversion ratio.

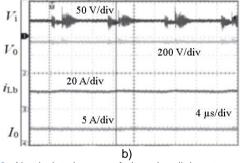

This chapter compares two topologies of DC/DC boost converters: non-isolated current-fed half-bridge and isolated current-fed push-pull converters. A current-fed push-pull dc/dc boost converter is shown in Fig. 9a. This converter is derived from a current-fed push-pull converter [12]. Additional diodes  $D_1$ ,  $D_2$ , and the capacitor  $C_1$  act as a regenerative snubber, recycled energy is stored in a leakage inductance of the push-pull transformer. Also, the series connection of all capacitors improves the voltage conversion ratio. Fig. 9b) confirms the converter's potential to obtain high voltage and output power.

In order to verify the operation of the proposed converter and the optimization methods analyzed theoretically above, a laboratory prototype has been assembled and tested. The specifications and parameters of the converter are shown in Table 8. The converter was supplied by a voltage (35-48) V and operated at a switching frequency 46 kHz, in a power range (950-2900) W, with a duty cycle D = (0.52-0.78) and an output voltage (315-530) V.

**Fig. 9.** Non-isolated current-fed push-pull boost converter: a) circuit, b)  $V_i$ - input voltage,  $V_o$ - output voltage,  $I_{Lb}$ - input current, and  $I_0$ - output current

**TABLE 8.** Main specifications and components of the current-fed push-pull DC/DC boost converter prototype

| Description              | Values                                                         |

|--------------------------|----------------------------------------------------------------|

| Input voltage source     | 10 PV module KD320GH-4YB                                       |

| PV array                 | in parallel: 3.2 kW at 1000 W/m <sup>2</sup>                   |

| Inductor $L_{\rm b}$     | 100 μH, ETD59/31/22-3F3, 10 turns,                             |

|                          | <i>δ</i> =1 mm                                                 |

| Switching frequency      | 46 kHz                                                         |

| Switches $S_1$ and $S_2$ | IRFP4668PBF(200 V/130A/8m $\Omega$ )                           |

| Diodes $D_1$ - $D_4$     | SDT12S60 SiC/600 V/12 A/1,5 V/30 nC                            |

| Capacitors $C_1$ - $C_3$ | $470 \mu F/250 V/130 m\Omega$ electrolytic                     |

| Transformer $T_{\rm r}$  | RTF-63×38×2; $n_{p1}$ = $n_{p2}$ =8 turns Litz                 |

|                          | $50 \times 0.35$ mm, $n_s = 16$ turns Litz $25 \times 0.35$ mm |

Figure 10 shows the efficiency of the current-fed push-pull converter in the range between (935-2840) W of output power at the switching frequency  $f_s$ =46 kHz, duty cycle D=0.6, and the previously discussed, as shown in Fig. 7, efficiency curve of the partially parallel converter. The efficiency for the lower power value was equal to 92.8% for the upper 84.4%. Peak efficiency reached 94,3% for an output equal to 1350 W, and with an input voltage of 48 V. At the low input voltage of 35 V and a power level of 2100 W, the efficiency was 90.5%. The losses in the inductive elements comprise 24% of total losses. In the tested converter, at 1350 W, switching losses account for almost half of total losses.

**Fig. 10.** Measured efficiency  $\eta$  of non-isolated current fed half-bridge and isolated current-fed push-pull boost converters as a function of output power P<sub>o</sub>, D=0.6

# C. Multi-phase interleaved boost-flyback DC-DC converter

The experiments showed that neither the boost topology nor the flyback topology in interleaved connections meet the condition of high efficiency and high voltage conversion ratio. On the other hand, the combination of the tapped boost converter and the boost-flyback converter fulfilled the

Fig. 11. Configuration of an n-phase interleaved boost-flyback converter: a) circuit, b) current and voltage waveforms in a single converter section for  $V_i$  = 40 V and  $R_o$  = 82  $\Omega$

expectations [23]. The benefits of this approach are demonstrated by a multi-phase interleaved boost-flyback converter design. As power densities continue to rise, interleaved boost designs become an effective tool to keep input currents manageable and increase efficiency while still maintaining good power density. Fig. 11 shows the circuit configuration of two modules in an n-phase interleaved boost-flyback converter with high step-up voltage conversion. A single converter module consists of a boost circuit ( $S_1$ ,  $L_{\rm P1}$ ,  $D_{\rm 11}$  and  $C_{\rm L}$ ) and a flyback circuit ( $S_1$ ,  $L_{\rm P1}$ ,  $L_{\rm S1}$ ,  $D_{\rm 21}$  and  $C_{\rm 2}$ ). Due to this connection, the converter output voltage  $V_0$  assumes the sum of boost and flyback output voltages.

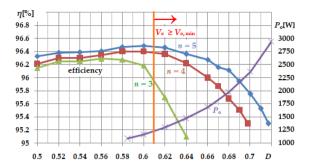

Theoretical considerations and experimental studies [13] of this converter showed high efficiency and a high voltage conversion ratio for several kilowatts of output power (Fig. 11.b). By splitting the input current into several power paths, conduction losses  $(I^2R)$  can be reduced, increasing overall efficiency compared to a single-phase converter. Because the five phases are connected to the output capacitors, the effective ripple frequency is five times higher, making ripple voltage reduction much easier. In order to verify the operation principle of the proposed converter, a laboratory prototype has been assembled and tested. The specifications and parameters of the laboratory prototype of the boost-flyback converter are shown in Table 9. In practical applications, e.g., in photovoltaic systems, efficiency and output power levels achieved with an output voltage of  $V_0 \ge 350$  V are useful. Fig. 12 shows the results of the converter efficiency measurement in configurations from 3 to 5 sections with of load resistance  $R_0 = 96 \Omega$  [13]. Fig. 12 also shows the diagrams of the output power  $P_0$  of the five-section converter obtained during the simulation of the model. The right part of the half-plane from the vertical line D = 0.61 corresponds to the ranges of efficiency and output power at the output voltage above  $V_{o,min}$ , where  $V_{o,min}$

TABLE 9. Interleaved boost-flyback converter components

| Output power of 5 sections $P_0 = 3.2 \text{ kW}$ | Compo-<br>nent        | Туре     | Specification           |

|---------------------------------------------------|-----------------------|----------|-------------------------|

| Input voltage $V_i = 40 \text{ V}$                | Inductor $L_{\rm Pl}$ | -        | 78 μΗ                   |

| Max. input current $I_{i,av} = 15.2 \text{ A}$    | Switch S <sub>1</sub> | IRFP4668 | 200 V/130 A/8<br>mΩ     |

| Input current ripple $\Delta I_{i(\%)} < 30\%$    | Diode $D_{21}$        | C3D20060 | 600 V/13/26 A/<br>1.8 V |

| Output voltage $V_0 = 350 \text{ V}$              | Diode $D_{21}$        | C3D04060 | 600 V/4 A/1.8<br>V      |

| Efficiency η> 95%                                 | Capacitor $C_2$       | PCPW245  | 60 μF/450 V/<br>3.8 mΩ  |

**TABLE 10.** Converter output power depending on the number of sections

|             | n = 3          |                  | n = 4          |                  | n = 5          |                  |

|-------------|----------------|------------------|----------------|------------------|----------------|------------------|

| $R_{\rm o}$ | $P_{ m o,min}$ | $P_{ m o,max}$   | $P_{ m o,min}$ | $P_{ m o,max}$   | $P_{ m o,min}$ | $P_{ m o,max}$   |

| $\Lambda_0$ | [W]            | [W]              | [W]            | [W]              | [W]            | [W]              |

| 65 Ω        | 1900           | $P_{ m o,nom,3}$ | 1500           | 1620             | 1280           | 1570             |

| 82 Ω        | 1910           | $P_{ m o,nom,4}$ | 1500           | $P_{ m o,nom,4}$ | 1280           | $P_{ m o,nom,4}$ |

| 96 Ω        | 1920           | $P_{ m o,nom,5}$ | 1500           | $P_{ m o,nom,5}$ | 1340           | 3050             |

Fig. 12. The results of multi-phase interleaved boost-flyback DC-DC converter efficiency  $\eta$  measurements for n = 3, 4, 5 sections compared with the output power Po as a function of the duty cycle D, with load resistance Ro = 96  $\Omega$ .

= 350 V. Table 10 summarises the output power ranges corresponding to the efficiency  $\eta \geq 0.95$  depending on the load resistance  $R_{\rm o}$  and the number of sections n. The minimum values of the output power ranges ( $P_{\rm o,min}$ ) correspond to the output voltage  $V_{\rm o} \geq V_{\rm o,min}$ , and the maximum power levels ( $P_{\rm o,max}$ ) are limited by the rated powers or the minimum efficiency value  $\eta_{\rm min} = 0.95$ . Since the nominal power of the five-section converter is  $P_{\rm o,nom,5} = 3200$  W, the corresponding power values for the four and three sections are  $P_{\rm o,nom,4} = 2560$  W and  $P_{\rm o,nom,3} = 1920$  W. Parameter  $P_{\rm E,n} = (\Delta P_{\rm o}/P_{\rm o,nom,n})100\%$  determines the percentage share of  $\Delta P_{\rm o}$  in the nominal power depending on the number of sections.

The analysis of the data contained in Table 10 shows that the conditions of the hypothetical efficiency ( $\eta \ge 0.95$ ) and output voltage ( $V_0 \ge 350 \text{ V}$ ) of the processed power  $\Delta P_0$  are met in the range from 650 W (n = 3) to 1710 W (n = 5) at the load of 82  $\Omega$  and 96  $\Omega$ . The percentage share of  $P_{\rm E,4}$  =  $P_{\rm E.5} = 53\%$  in the nominal powers of a four- and five-section converter signals the necessity to consider the number of designed sections of the interleaved boost-flyback converter. During laboratory tests, about 75% share of losses in semiconductor elements in total power losses was found, including about 50% in both diodes. Losses in the coupled inductor do not exceed 25%, and in output capacitors, they are less than 0.5% of total losses. As the number of sections increases, the share of losses in the winding resistances of the coupled inductors decreases. The use of smaller active and passive elements (output filter capacitors and inductors) is shown to improve the power

**TABLE 11.** List of basic parameters of the tested non-isolated converters (at maximum efficiency point)

| Conver.                                         | η    | $P_{o(max)}$ | $V_i$ | $B_{ m theoret}$   | S | D  |  |

|-------------------------------------------------|------|--------------|-------|--------------------|---|----|--|

| -                                               | [%]  | [W]          | [V]   | [V/V]              | ı | •  |  |

| Dual<br>inductor-<br>fed                        | 95.8 | 1650         | 31    | $\frac{1+2n}{1-D}$ | 2 | 4  |  |

| Current-fed push-pull                           | 94.3 | 1350         | 48    | $\frac{2n}{1-D}$   | 2 | 4  |  |

| Multi-phase<br>interleaved<br>boost-<br>flyback | 96.5 | 2870         | 40    | $\frac{4n}{1-D}$   | 5 | 10 |  |

= 0.6, S - number of transistors, D - number of diodes

density. The converter was integrated with a 3.2 kW low-voltage photovoltaic panel and was verified with the implemented MPPT algorithm on a laboratory stand [24]. Table 11 presents the summarized information on the studied non-isolated converters for the operating point yielding maximum efficiency. The exhibited converters allow are performing well, especially considering the notable transferred power of over 1 kW.

## 4. DISCUSION & CONCLUSION

This publication discusses the results of the research on the possibilities of reducing power losses in the energy conversion process and the selection of boost DC/DC converters to interface low-voltage high-power supply to the power grid. During the practical implementation of the project, answers to the questions posed in the introduction to the article were obtained. The discussion mainly involves the performance of the modified isolated and the new non-isolated circuits in relation to the known topologies.

It has been shown that in systems powered by low-voltage energy sources with high input currents, it is possible to achieve high efficiency ( $\eta$ > 96%) and the required DC voltage conversion ratio (10-20), without the need to work with the maximum values of the duty ratio (D < 0.7), with both insulated and non-insulated converters. Previously, it was considered that meeting these three requirements was only possible with isolated converters.

The tests of boost converters for coupling low-voltage high power supply with the grid show that the highest efficiency, 96.6%, was achieved in the non-isolated fivephase interleaved boost-flyback DC-DC converter. In contrast, non-isolated push-pull, isolated half-bridge, and partial parallel converters have slightly lower efficiency but gain in size as the number of components is reduced. They also provide better utilization of switches, have a better voltage conversion ratio, and are able to work at a lower duty cycle than other boost converters. Boost converters are usually equipped with overvoltage protection circuits. In some selected topologies, the over-voltage protection circuits are useless since inductive components and the circuit configuration are optimized to work under low input voltage and high power. In other converters, the energy stored in the leakage inductance of inductive components is transferred to the output capacitors, and that eliminates voltage overshoots across power switches.

An analysis of transformer leakage inductance shows that not only does it not depend on the transformer turns ratio, but the extensive interleaving of primary and secondary windings needed to reduce the proximity effect significantly reduces transformer leakage energy. High power and low input voltage cause the converter input impedance to be very low. That requires low values for effective  $R_{\rm ac}$  resistance and parasitic inductance dissipation to achieve high efficiency of energy conversion.

A high input current requires a large area of crosssectional winding inductors. To avoid the serious consequences of the proximity effect, a minimum possible number of layers of windings must be properly positioned and interleaved in sections. In both isolated and nonisolated boost converters, very low leakage inductance and very low energy in the inductive components can be achieved, contrary to generally accepted views, through the proper design of magnetic components. Oversizing the rated voltage of power switches leads to a sharp increase in conduction losses. The highest efficiency can be achieved by using switches with lower blocking voltage values. The possibility of using smaller active and passive elements (output filter capacitors and inductors) has been demonstrated to improve the power density of interleaved converters. Power switches in interleaved converters, compared to the switches used in non-interleaved ones, work at lower values of effective currents. This allows the use of switches with better static and dynamic parameters during parallel work. The difficulty in controlling the interleaved converters entails providing the same cycle for all transistors. Even a slight difference in cycles may lead to imbalance and reduce system reliability. In spite of the cost higher than that of conventional converters of interleaved power converters, the potential gain of efficiency will bring tangible economic effects throughout the lifetime of the converter. The use of boost modular converters can improve the efficiency of energy conversion systems, e.g., photovoltaic ones. When designing modular converters, theoretically, the output power is not limited.

The figure of merit indicates a large potential in the application of SiC [2, 25, 26] devices in low-voltage, high-power boost converters. The application of SiC Schottky diodes in output circuits eliminates the reverse recovery problems and thus allows quick diode turn-off without significant power losses. Still, no SiC transistors, which have a lower drain resistance than the low-voltage Si MOSFET counterparts, are available on the market. Achieving low-voltage converters with a power of several kW of efficiency higher than 96% becomes possible if we use transistors with a drain-source resistance of several m $\Omega$ , a maximum switching frequency of several dozen kHz, using multi-section topologies with a parallel flow of input currents and magnetic elements with a low inductance distraction.

Finally, it should be noted that an interesting solution in the discussed converters is using GaN transistors [27]. The devices are claimed to have the lowest  $R_{DS,on}$  FETs in the market at 150 V and 200 V, respectively, in a size that is 15 times smaller than alternative silicon MOSFETs. In addition to offering devices with half the on-resistance and 15 times smaller,  $Q_{\rm G}$ ,  $Q_{\rm GD}$ ,  $Q_{\rm OSS}$  are more than three times smaller than Si MOSFETs, and the reverse recovery charge  $(Q_{RR})$  is zero. These properties result in switching losses, ringing, and overshooting that are lower than in hardswitched silicon solutions. Simulation studies of the GaN converters discussed above showed the possibility of increasing the efficiency by several percent. Thus, this technology should be further investigated for low-voltage DC/DC converters in the future, as the technology is constantly progressing and better and cheaper power devices are introduced into the market.

### **ACKNOWLEDGEMENTS**

This work was supported by the Research Project WZ/WE-IA/6/2023 funded by The Scientific Subsidy of the Ministry of Science and Higher Education (MNiSW)

#### REFERENCES

- [1] S. Umamaheswari, R. Karthigaivel, G. Satheesh Kumar, and N. Vengadachalam, "A novel revolutionary substantial transformative control technique for solar fed-full bridge converter based energy stabilization for grid connected applications," *Bull. Pol. Acad. Sci. Tech. Sci.*, vol. 70, no. 2, p. e140517, 2022, doi: 10.24425/bpasts.2022.140517.

- [2] M. Harasimczuk, R. Kopacz, P. Trochimiuk, R. Miśkiewicz, and J. Rąbkowski, "Experimental Investigation on SiC MOSFET Turn-Off Power Loss Reduction Using the Current Sink Capacitor Technique," *Energies*, vol. 17, no. 1, p. 189, 2024, doi: 10.3390/en17010189.

- [3] H. Tarzamni, H.S. Gohari, M. Sabahi, and J. Kyyrä,

"Nonisolated High Step-Up DC–DC Converters: Comparative

Review and Metrics Applicability," *IEEE Trans.Power Electron.*, vol. 39, no. 1, pp. 582–625, 2024, doi:

10.1109/TPEL.2023.3264172.

- [4] M. Harasimczuk, "A QR-ZCS Boost Converter With Tapped Inductor and Active Edge-Resonant Cell," *IEEE Trans.Power Electron.*, vol. 35, no. 12, pp. 13085–13095, 2020, doi: 10.1109/TPEL.2020.2991363.

- [5] J. Dawidziuk and M. Harasimczuk, "A novel quasi-resonant ZVS boost converter with tapped inductor," *Bull. Pol. Acad. Sci. Tech. Sci. DOI - 10.24425/bpasts.2021.136043*, vol. 69, no. 1, pp. e136043-e136043, 26.01.2021 2021.

- [6] M. Harasimczuk, R. Kopacz, and A. Tomaszuk, "Lossless Clamp Circuit with Turn-off Voltage and Current Reduction in High Step-up DC/DC Converter with Coupled Inductor," *IEEE Trans. Power Electron.*, pp. 1–13, 2023, doi: 10.1109/TPEL.2023.3327064.

- [7] S. Hasanpour, Y.P. Siwakoti, and F. Blaabjerg, "A New High Efficiency High Step-Up DC/DC Converter for Renewable Energy Applications," *IEEE Trans. Ind. Electron.*, vol. 70, no. 2, pp. 14891500, 2023, doi: 10.1109/TIE.2022.3161798.

- [8] S. Hasanpour and S.S. Lee, "New Step-Up DC/DC Converter With Ripple-Free Input Current," *IEEE Trans. Power Electron.*, vol. 39, no. 2, pp. 2811–2821, 2024, doi: 10.1109/TPEL.2023.3336005.

- [9] M.O. Badawy, A.S. Yilmaz, Y. Sozer, and I. Husain, "Parallel Power Processing Topology for Solar PV Applications," *IEEE Transactions on Industry Applications*, vol. 50, no. 2, pp. 1245–1255, 2014, doi: 10.1109/TIA.2013.2277546.

- [10] R. K. Pachauri et al., "Impact of Partial Shading on Various PV Array Configurations and Different Modeling Approaches: A Comprehensive Review," *IEEE Access*, vol. 8, pp. 181375–181403, 2020, doi: 10.1109/ACCESS.2020.3028473.

- [11] L. Gao, R.A. Dougal, S. Liu, and A.P. Iotova, "Parallel-Connected Solar PV System to Address Partial and Rapidly Fluctuating Shadow Conditions," *IEEE Trans. Ind. Electron.*, vol. 56, no. 5, pp. 1548–1556, 2009, doi: 10.1109/TIE.2008.2011296.

- [12] A. Krupa, "Isolated DC/DC step-up converters powered by low-voltage energy sources," PhD Thesis, Faculty of Electrical Engineering, Bialystok University of Technnology, 2018

- [13] A. Tomaszuk, "Application of interleaved step-up DC/DC converters with coupled inductors in photovoltaic system," PhD Thesis, Faculty of Electrical Engineering, Bialystok University of Technology, 2018.

- [14] M. Harasimczuk, "Non-isolated quasi-resonant step-up converters with tapped inductors," PhD Thesis, Faculty of Electrical Engineering, Bialystok Univesity of Technology, 2010

- [15] E.N. da Silva, D. de Araújo Honório and R.P. Torrico Bascopé, "Modified Multiport Current-fed Push-Pull applied in power supplies for multilevel power converter," in 2021 14th IEEE International Conference on Industry Applications (INDUSCON), São Paulo, Brazil, 2021, pp. 545–546, doi: 10.1109/INDUSCON51756.2021.9529783.

- [16] Z. Zhang et al., "A Quasi-Switched-Capacitor-Based Bidirectional Isolated DC–DC Converter With High Voltage Conversion Ratio and Reduced Current Ripple," *IEEE Trans. Power Electron.*, vol. 39, no. 4, pp. 4426–4437, 2024, doi: 10.1109/TPEL.2023.3346396.

- [17] V.K. Goyal and A. Shukla, "Isolated DC–DC Boost Converter for Wide Input Voltage Range and Wide Load Range Applications," *IEEE Trans. Ind. Electron.*, vol. 68, no. 10, pp. 9527–9539, 2021, doi: 10.1109/TIE.2020.3029479.

- [18] X. Pan, H. Li, Y. Liu, T. Zhao, C. Ju, and A. K. Rathore, "An Overview and Comprehensive Comparative Evaluation of Current-Fed-Isolated-Bidirectional DC/DC Converter," *IEEE Trans. Power Electron.*, vol. 35, no. 3, pp. 2737–2763, 2020, doi: 10.1109/TPEL.2019.2931739.

- [19] A. Chub, D. Vinnikov, F. Blaabjerg, and F.Z. Peng, "A Review of Galvanically Isolated Impedance-Source DC–DC Converters," *IEEE Trans. Power Electron.*, vol. 31, no. 4, pp. 2808–2828, 2016, doi: 10.1109/TPEL.2015.2453128.

- [20] P. Xuewei and A.K. Rathore, "Current-Fed Soft-Switching Push–Pull Front-End Converter-Based Bidirectional Inverter for Residential Photovoltaic Power System," *IEEE Trans. Power Electron.*, vol. 29, no. 11, pp. 6041–6051, 2014, doi: 10.1109/TPEL.2014.2301495.

- [21] B. Boudjellal and T. Benslimane, "Study of an open-switch fault detection algorithm for a three-phase interleaved DC–DC boost converter in a photovoltaic system," *Arch. Electr. Eng.*, vol. 72, no. 3, pp. 661–676, 2023, doi: 10.24425/aee.2023.146043.

- [22] N. Perera, A. Jafari, R. Soleimanzadeh, N. Bollier, S.G. Abeyratne, and E. Matioli, "Hard-Switching Losses in Power FETs: The Role of Output Capacitance," *IEEE Trans. Power Electron.*, vol. 37, no. 7, pp. 7604–7616, 2022, doi: 10.1109/TPEL.2021.3130831.

- [23] B.R. Lin, C.H. Chao, and C.C. Chien, "Interleaved boost-flyback converter with boundary conduction mode for power factor correction," in 2011 6th IEEE Conference on Industrial Electronics and Applications, Beijing, China, 2011, pp. 1828–1833, doi: 10.1109/ICIEA.2011.5975889.

- [24] A. Tomaszuk and J. Dawidziuk, "Low Voltage Photovoltaic System with P-V Curve Evaluation MPPT Algorithm Implementation," *Prz. Elektrotechniczny*, vol. 90, no. 7, pp. 32–34, 2014, doi: 10.12915/pe.2014.07.05.

- [25] R. Kopacz, M. Harasimczuk, P. Trochimiuk, and J. Rabkowski, "Investigation of Soft-Switching QSW Technique in DC/DC SiC-Based Flying Capacitor Converter With Q2L Control," *IEEE Trans. Ind. Electron.*, vol. 70, no. 9, pp. 9035–9045, 2023, doi: 10.1109/TIE.2022.3212425.

- [26] R. Kopacz, M. Harasimczuk, P. Trochimiuk, G. Wrona, and J. Rąbkowski, "Medium Voltage Flying Capacitor DC–DC Converter With High-Frequency TCM-Q2L Control," *IEEE Trans. Power Electron.*, vol. 37, no. 4, pp. 4233–4248, 2022, doi: 10.1109/TPEL.2021.3122329.

- [27] A. Endruschat, C. Novak, H. Gerstner, T. Heckel, C. Joffe, and M. März, "A Universal SPICE Field-Effect Transistor Model Applied on SiC and GaN Transistors," *IEEE Trans. Power Electron.*, vol. 34, no. 9, pp. 9131–9145, 2019, doi: 10.1109/TPEL.2018.2889513.